Pci bus architecture tutorial pdf

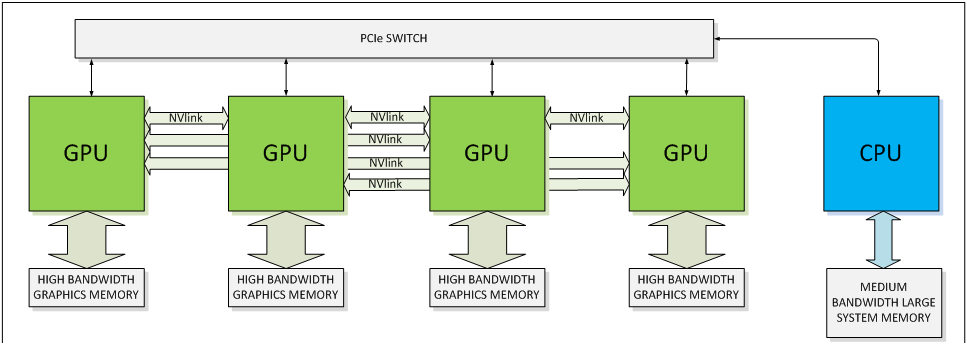

PCI bus overview • PCI bus – Conventional PCI •Developed and standardised in early 90’s •32 or 64 bit shared parallel bus •Up to 66MHz (533MB/s) – PCI-X •Up to 133MHz (1066MB/s) – PCI Express •Consists of serial p2p links •Software-compatible with conventional PCI •Up to 16GB/s per device. PCI bus overview: memory space CPU RAM PCI controller Dev1 Dev3 Dev1 Dev2 Dev3 Dev2

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

Introduction to PCI protocol Today’s computer systems, with their emphasis on high resolution graphics, full motion video, high bandwidth networking, and so on, go far beyond the capabilities of the architecture that ushered in the age of the personal computer in 1982.

These free resources are available to the Intel® Developer Network for PCI Express* Architecture community. PCI Express* Specifications. By downloading and reading these documents, you agree to the obligations set forth in the Intel® Developer Network for PCI Express* Architecture user agreement.

9 PCI BUS • Introduced by Intel in 1992, PCI is short for Peripheral Component Interconnect and is a 32-bit computer bus that is also available as a 64-bit bus today.

current PCI architecture serves the need. You can choose the modules that are the best fit for You can choose the modules that are the best fit for your applications, without being concerned whether they are using PCI or PCI Express signaling.

ISA (Industry Standard Architecture) — A transaction begins over the PCI bus — Each potential target on the bus decodes the transaction’s PCI address to determine whether it belongs to that target’s assigned address space – One target may be assigned a larger address space than another, and would thus respond to more addresses — The target that owns the PCI address then claims

Watchdog timer attached to PCI bus (part of the Intel i6300ESB chipset). Two cascaded, programmable timers (“stages”). When first stage times out, second stage …

Understanding PCI Bus, PCI-Express and In finiBand Architecture Contrasting The Architectures Mellanox Technologies Inc 2 Rev 1.20 slots. The following table highlights the key featur es that distinguish Infi niBand from simple local bus architectures such as PCI and PCI-Express: As can be seen from the table above, the InfiniBand architecture supports features that make it substantially …

Description : With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

0 Bus Based Platforms.Obtaining PCI Bus Specifications. Chapter 2: Intro to PCI Bus Operation. Promotes PCI as an industry-wide standard. Transaction Completion and pamietnik ksiezniczki pdf Return of Bus to Idle State.als, because these days the PCI bus is the most

Realistic PC architecture Advanced Programable Interrupt Controller bus I/O APIC CPU Bridge Main memory North bus side front-South Bridge bus ISA CPU USB bus AGP PCI

Pci bus tutorial pdf WordPress.com

pci-pci-bus-numbering The Linux Documentation Project

Using PCI, a computer can support both new PCI cards while continuing to support Industry Standard Architecture expansion cards, an older standard. Designed by Intel, the original PCI was similar to the VESA Local Bus .

pci bus demystified second edition by doug abbott amsterdam • boston • heidelberg • london new york • oxford • paris • san diego san francisco • singapore • sydney • tokyo

Conventional PCI, often shortened to PCI, is a local computer bus for attaching hardware devices in a computer. PCI is the acronym for Peripheral Component Interconnect and is part of the PCI Local Bus …

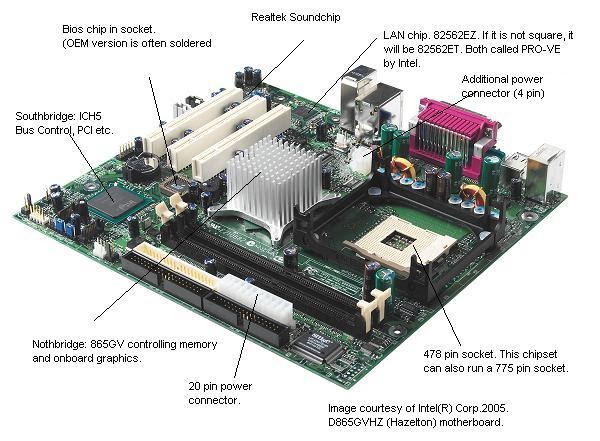

PCI uses a shared bus topology to allow for communication among the different devices on the bus; the different PCI devices (i.e., a network card, a sound card, a RAID card, etc.) are all attached to the same bus, which they use to communicate with the CPU. Take a look at the following diagram to get a feel for what a shared bus looks like.

Amazon Web Services – Standardized Architecture for PCI DSS December 2016 Page 9 of 35 Amazon Glacier – Amazon Glacier is a storage service for archiving and long-term backup of infrequently used data. It provides secure, durable, and extremely low-cost storage, supports data transfer over SSL, and automatically encrypts data at rest. With Amazon Glacier, you can store your …

If the PCI device that was found was a PCI-PCI bridge then a pci_bus data structure is built and linked into the tree of pci_bus and pci_dev data structures pointed at by pci_root. The PCI initialisation code can tell if the PCI device is a PCI-PCI Bridge because it has a class code of 0x060400 .

Figure 16: Address translation from PCI-EXPRESS bus address to AMBA Address….. 27 Figure 17: PCI AMBA Advanced Microcontroller Bus Architecture – On-Chip Communication Bus APB Advanced Peripheral Bus – AMBA standard bus for Low-power peripherals ASB Advanced System Bus – AMBA standard bus for High-performance ATX Advanced Technology Extended – motherboard form …

With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

PCI bus ISA bus Socket-7 for processor South bridge North bridge Video adaptor DRAM IDE bus Video memory Level-2 cache

For example, through the mechanical architecture, the system controller is defined to be in the leftmost slot of a PXI chassis to ensure it is at the left end of the PCI bus segment. It simplifies the integration and increases the degree of compatibility between chassis …

STANDARD I/O INTERFACES . The processor bus is the bus defied by the signals on the processor chip . itself. Devices that require a very high-speed connection to the processor, such as the

26/03/2017 · In this video, we discuss the basics of PCI – Type0/1 headers and bus enumeration, so that we can easily transition to PCIe. Understanding of …

PCI architecture allows bus mastering of multiple devices on the bus simultaneously, with the arbitration circuitry working to ensure that no device on the bus …

• A data bus of 32-bits fetches, loads, or stores the instruction or data of 32-bits at one time Schaum’s Outline of Theory and Problems of Computer Architecture

PC-based instrumentation and microcontrollers Computer buses and interfaces the capacity of a desktop computer with a PCI/PCIe bus. • One of the most important benefits PXI offers is its integrated timing and triggering features. Without any external connections, multiple devices can be synchronized by using the internal buses resident on the backplane of a PXI chassis • By taking

• PCI Power Management, USB, Cardbus, PCI Express, etc. • L1 state is the required link power state in both of these D-states. 23 March 11, 2007 File: chalupsky_01_0307 Device Power States (cont.) D3 (Off): • D3 hot Primary power is not yet removed from the device. D3 hot maps to L1 to support clock removal on mobile platforms. PCI Bus clock is running. • D3 cold Primary power may

Architecture Tutorial Alan Goodrum Chairman, PCI-X Workgroup Staff Fellow, Compaq Computer Corporation May 23, 2000 Applied Computing Conference 2000

Standardized Architecture for PCI DSS on the AWS Cloud

Eli Billauer The anatomy of a PCI/PCI Express kernel driver. Introduction Part I: The hardware The Strategy Part II: Code highlights Introduction Eli Billauer The anatomy of a PCI/PCI Express kernel driver. Introduction Part I: The hardware The Strategy Part II: Code highlights Overview Kernel programming is copying from people knowing better than you. Reading PCI/PCIe drivers is being told

PCI-X, PCI-express to name a (relevant) few. All the bus types we will detail are vari- All the bus types we will detail are vari- ants of the PCI bus type, however some of …

Pcie tutorial pdf Pcie tutorial pdf Pcie tutorial pdf DOWNLOAD! DIRECT DOWNLOAD! Pcie tutorial pdf Yet PCI Express architecture is significantly different from its predecessors PCI. 0 PHYs may optionally support 5 GTs signaling,

Based on existing PCI architecture ¾Conventional 33/66 MHz PCI adapters can be used in PCI-X slots ¾PCI-X adapters can be used in conventional PCI slots Provides two speed grades: 66 MHz and 133 MHz ¾The slowest board dictates the maximum speed on a particular bus ! Targeted at high-end data networking and storage network applications . February 2003 Page 9 PCI-X 2.0 Based on PCI-X …

computer buses such as PCI bus and VMEbus. In fact, the WISHBONE architecture is analogous to a microcomputer bus in that that they both: (a) offer a flexible integration solution that can be easily tailored to a specific application; (b)

architecture. Number of embedded devices in a computer system use PCI Three standards for the devices interfacing with the PC Peripheral Component Interconnect (PCI) Bus. 2008 Chapter-3 L22: “Embedded Systems – ” , Raj Kamal, Publs.: McGraw-Hill Education 13 PCI 32bit/33 MHz, and 64bit/66 MHz PCI Extended (PCI/X) 64 bit/100 MHz , Compact PCI (cPCI) Bus Two super speed versions PCI …

PCI Bus Operation A guide for the uninformed by the slightly less uninformed! E. Hazen – 09/17/99 PCI Fundamentals The PCI bus is the de-facto standard bus for current-generation personal computers. – stanley yelnats survival guide to camp green lake use the PCI testbench, you should have a basic understanding of PCI bus architecture and operations. f Refer to the PCI MegaCore Function User Guide for information on the

The PCI bus was introduced to the standard PC architecture in the early 90’s and has maintained its dominance with only one major upgrade during that period: from 32 bit/33 MHz to 64bit/66Mhz. The PCI-X initiative takes this one step further to 133MHz and seemingly should provide the PCI architecture with a few more years of life. But there is a divergence between what personal computers and

Abstract – PCI (Peripheral Component Interconnect) is a computer bus for attaching hardware devices in a computer. Work on PCI first began at Intel’s Architecture Development Lab, circa 1990.

*Some architectures also display the PCI domain information in the/proc/pci and/proc/bus/pci files. ,ch12.1659 Page 303 Friday, January 21, 2005 3:08 PM This is the Title of the Book, eMatter Edition

A Peripheral Component Interconnect Bus (PCI bus) connects the CPU and expansion boards such as modem cards, network cards and sound cards. These expansion boards are normally plugged into expansion slots on the motherboard.

A transaction begins over the PCI bus Each potential target on the bus decodes the transaction’s PCI address to determine whether it belongs to that target’s

Basic Bus Architecture Add-in Cards Processor Processor 56K 56K System Modem Modem ISA System MPEG MPEG Expansion Expansion Host Host 3D 3D Sound Sound Video Video Bus Bus Bridge Bridge Card Card Capture Capture Bridge Bridge Card Card PCI PCI Local Local Bus Bus 3

13-slot PXI system can be built using a single PCI-PCI bridge. The PXI specification The PXI specification adds electrical features that meet the high-performance requirements of

Refer to the following table for PCI bus architecture performance capabilities. A standard PCI bus can be up to four slots. Each slot can be any combination listed on the chart below. Electrical signaling is an important part of the PCI specification. The PCI signal is a “reflective” signal meaning that the signal travels to the end of the bus, and as the reflection travels back the other

2 • PCI Express Port Bus Driver Support for Linux per PCI Express Port. However, this solution would lack the ability to have each service built

information on bus architectures and bus protocols, and then provides specific information on various industry standard bus architectures from the past and the present, and their advantages and disadvantages. It also describes how different types of bus architectures are used simultaneously in different parts of a modern personal computer. 1. Introduction A typical computer system is …

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

Rev. 1.0 Sys MFG T/ED 4/25/2003 PC Architecture For Technicians Level-1 Technical Excellence Development Series Ch 14 – Page 7 Introduction lThe PCI Bus Solution

PCI bus provides a bus architecture that also supports peripherals and devices like Hard Disk Drives, Networks etc. PCI successfully replaced all other older buses like ISA, EISA and VL . PCI has various features. It is the only bus that can carry 64 bits of data in each clock cycle which makes it useful for Pentium processor family.

Introduction to PCI protocol electrofriends.com

PCI Tutorial 1/31/00 vs 1 TU Clausthal

Introduction to the PXI Architecture National Instruments

Implementing a PCI-Express AMBA interface controller on a

Pcie tutorial pdf WordPress.com

Epics Driver/Device Support Tutorial Stanford University

Hardware Implementation of PCI Interface Using Verilog & FPGA

WWW.TESTBENCH.IN

fallout shelter handbook by chuck west – WISHBONE System-on-Chip (SoC) Interconnection Architecture

Bus Architectures EOLSS

What is Peripheral Component Interconnect Bus (PCI Bus

XPRESS PECIFICATION T pxisa.org

What is PCI (Peripheral Component Interconnect

PCI Tutorial 1/31/00 vs 1 uml.edu

• A data bus of 32-bits fetches, loads, or stores the instruction or data of 32-bits at one time Schaum’s Outline of Theory and Problems of Computer Architecture

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

9 PCI BUS • Introduced by Intel in 1992, PCI is short for Peripheral Component Interconnect and is a 32-bit computer bus that is also available as a 64-bit bus today.

PCI architecture allows bus mastering of multiple devices on the bus simultaneously, with the arbitration circuitry working to ensure that no device on the bus …

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

0 Bus Based Platforms.Obtaining PCI Bus Specifications. Chapter 2: Intro to PCI Bus Operation. Promotes PCI as an industry-wide standard. Transaction Completion and pamietnik ksiezniczki pdf Return of Bus to Idle State.als, because these days the PCI bus is the most

Conventional PCI, often shortened to PCI, is a local computer bus for attaching hardware devices in a computer. PCI is the acronym for Peripheral Component Interconnect and is part of the PCI Local Bus …

Watchdog timer attached to PCI bus (part of the Intel i6300ESB chipset). Two cascaded, programmable timers (“stages”). When first stage times out, second stage …

Eli Billauer The anatomy of a PCI/PCI Express kernel driver. Introduction Part I: The hardware The Strategy Part II: Code highlights Introduction Eli Billauer The anatomy of a PCI/PCI Express kernel driver. Introduction Part I: The hardware The Strategy Part II: Code highlights Overview Kernel programming is copying from people knowing better than you. Reading PCI/PCIe drivers is being told

Introduction to PCI protocol Today’s computer systems, with their emphasis on high resolution graphics, full motion video, high bandwidth networking, and so on, go far beyond the capabilities of the architecture that ushered in the age of the personal computer in 1982.

• PCI Power Management, USB, Cardbus, PCI Express, etc. • L1 state is the required link power state in both of these D-states. 23 March 11, 2007 File: chalupsky_01_0307 Device Power States (cont.) D3 (Off): • D3 hot Primary power is not yet removed from the device. D3 hot maps to L1 to support clock removal on mobile platforms. PCI Bus clock is running. • D3 cold Primary power may

PCI uses a shared bus topology to allow for communication among the different devices on the bus; the different PCI devices (i.e., a network card, a sound card, a RAID card, etc.) are all attached to the same bus, which they use to communicate with the CPU. Take a look at the following diagram to get a feel for what a shared bus looks like.

Refer to the following table for PCI bus architecture performance capabilities. A standard PCI bus can be up to four slots. Each slot can be any combination listed on the chart below. Electrical signaling is an important part of the PCI specification. The PCI signal is a “reflective” signal meaning that the signal travels to the end of the bus, and as the reflection travels back the other

Computer Bus Architecture christie alwis

WWW.TESTBENCH.IN

pci bus demystified second edition by doug abbott amsterdam • boston • heidelberg • london new york • oxford • paris • san diego san francisco • singapore • sydney • tokyo

PCI Bus Operation A guide for the uninformed by the slightly less uninformed! E. Hazen – 09/17/99 PCI Fundamentals The PCI bus is the de-facto standard bus for current-generation personal computers.

Watchdog timer attached to PCI bus (part of the Intel i6300ESB chipset). Two cascaded, programmable timers (“stages”). When first stage times out, second stage …

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

computer buses such as PCI bus and VMEbus. In fact, the WISHBONE architecture is analogous to a microcomputer bus in that that they both: (a) offer a flexible integration solution that can be easily tailored to a specific application; (b)

PC Architecture Napier

Memory and I/O buses Stanford University

Conventional PCI, often shortened to PCI, is a local computer bus for attaching hardware devices in a computer. PCI is the acronym for Peripheral Component Interconnect and is part of the PCI Local Bus …

Based on existing PCI architecture ¾Conventional 33/66 MHz PCI adapters can be used in PCI-X slots ¾PCI-X adapters can be used in conventional PCI slots Provides two speed grades: 66 MHz and 133 MHz ¾The slowest board dictates the maximum speed on a particular bus ! Targeted at high-end data networking and storage network applications . February 2003 Page 9 PCI-X 2.0 Based on PCI-X …

PCI bus provides a bus architecture that also supports peripherals and devices like Hard Disk Drives, Networks etc. PCI successfully replaced all other older buses like ISA, EISA and VL . PCI has various features. It is the only bus that can carry 64 bits of data in each clock cycle which makes it useful for Pentium processor family.

2 • PCI Express Port Bus Driver Support for Linux per PCI Express Port. However, this solution would lack the ability to have each service built

*Some architectures also display the PCI domain information in the/proc/pci and/proc/bus/pci files. ,ch12.1659 Page 303 Friday, January 21, 2005 3:08 PM This is the Title of the Book, eMatter Edition

PCI Tutorial Electronics Physical Layer Protocols

PXI Specification PCI eXtensions for Instrumentation

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

current PCI architecture serves the need. You can choose the modules that are the best fit for You can choose the modules that are the best fit for your applications, without being concerned whether they are using PCI or PCI Express signaling.

Amazon Web Services – Standardized Architecture for PCI DSS December 2016 Page 9 of 35 Amazon Glacier – Amazon Glacier is a storage service for archiving and long-term backup of infrequently used data. It provides secure, durable, and extremely low-cost storage, supports data transfer over SSL, and automatically encrypts data at rest. With Amazon Glacier, you can store your …

9 PCI BUS • Introduced by Intel in 1992, PCI is short for Peripheral Component Interconnect and is a 32-bit computer bus that is also available as a 64-bit bus today.

PCI bus provides a bus architecture that also supports peripherals and devices like Hard Disk Drives, Networks etc. PCI successfully replaced all other older buses like ISA, EISA and VL . PCI has various features. It is the only bus that can carry 64 bits of data in each clock cycle which makes it useful for Pentium processor family.

Abstract – PCI (Peripheral Component Interconnect) is a computer bus for attaching hardware devices in a computer. Work on PCI first began at Intel’s Architecture Development Lab, circa 1990.

STANDARD I/O INTERFACES . The processor bus is the bus defied by the signals on the processor chip . itself. Devices that require a very high-speed connection to the processor, such as the

13-slot PXI system can be built using a single PCI-PCI bridge. The PXI specification The PXI specification adds electrical features that meet the high-performance requirements of

PCI bus overview • PCI bus – Conventional PCI •Developed and standardised in early 90’s •32 or 64 bit shared parallel bus •Up to 66MHz (533MB/s) – PCI-X •Up to 133MHz (1066MB/s) – PCI Express •Consists of serial p2p links •Software-compatible with conventional PCI •Up to 16GB/s per device. PCI bus overview: memory space CPU RAM PCI controller Dev1 Dev3 Dev1 Dev2 Dev3 Dev2

WWW.TESTBENCH.IN

The History of the PCI Bus Architecture NComm

PCI bus ISA bus Socket-7 for processor South bridge North bridge Video adaptor DRAM IDE bus Video memory Level-2 cache

Realistic PC architecture Advanced Programable Interrupt Controller bus I/O APIC CPU Bridge Main memory North bus side front-South Bridge bus ISA CPU USB bus AGP PCI

A transaction begins over the PCI bus Each potential target on the bus decodes the transaction’s PCI address to determine whether it belongs to that target’s

PCI Bus Operation A guide for the uninformed by the slightly less uninformed! E. Hazen – 09/17/99 PCI Fundamentals The PCI bus is the de-facto standard bus for current-generation personal computers.

PCI bus overview • PCI bus – Conventional PCI •Developed and standardised in early 90’s •32 or 64 bit shared parallel bus •Up to 66MHz (533MB/s) – PCI-X •Up to 133MHz (1066MB/s) – PCI Express •Consists of serial p2p links •Software-compatible with conventional PCI •Up to 16GB/s per device. PCI bus overview: memory space CPU RAM PCI controller Dev1 Dev3 Dev1 Dev2 Dev3 Dev2

pci bus demystified second edition by doug abbott amsterdam • boston • heidelberg • london new york • oxford • paris • san diego san francisco • singapore • sydney • tokyo

Linux Graphics Drivers an Introduction freedesktop.org

Implementing a PCI-Express AMBA interface controller on a

PCI-X, PCI-express to name a (relevant) few. All the bus types we will detail are vari- All the bus types we will detail are vari- ants of the PCI bus type, however some of …

The PCI bus was introduced to the standard PC architecture in the early 90’s and has maintained its dominance with only one major upgrade during that period: from 32 bit/33 MHz to 64bit/66Mhz. The PCI-X initiative takes this one step further to 133MHz and seemingly should provide the PCI architecture with a few more years of life. But there is a divergence between what personal computers and

pci bus demystified second edition by doug abbott amsterdam • boston • heidelberg • london new york • oxford • paris • san diego san francisco • singapore • sydney • tokyo

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

Architecture Tutorial Alan Goodrum Chairman, PCI-X Workgroup Staff Fellow, Compaq Computer Corporation May 23, 2000 Applied Computing Conference 2000

Description : With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

Basic Bus Architecture Add-in Cards Processor Processor 56K 56K System Modem Modem ISA System MPEG MPEG Expansion Expansion Host Host 3D 3D Sound Sound Video Video Bus Bus Bridge Bridge Card Card Capture Capture Bridge Bridge Card Card PCI PCI Local Local Bus Bus 3

• A data bus of 32-bits fetches, loads, or stores the instruction or data of 32-bits at one time Schaum’s Outline of Theory and Problems of Computer Architecture

*Some architectures also display the PCI domain information in the/proc/pci and/proc/bus/pci files. ,ch12.1659 Page 303 Friday, January 21, 2005 3:08 PM This is the Title of the Book, eMatter Edition

computer buses such as PCI bus and VMEbus. In fact, the WISHBONE architecture is analogous to a microcomputer bus in that that they both: (a) offer a flexible integration solution that can be easily tailored to a specific application; (b)

PCI Testbench User Guide intel.com

COMP9242 2010/S2 Week 7

*Some architectures also display the PCI domain information in the/proc/pci and/proc/bus/pci files. ,ch12.1659 Page 303 Friday, January 21, 2005 3:08 PM This is the Title of the Book, eMatter Edition

• PCI Power Management, USB, Cardbus, PCI Express, etc. • L1 state is the required link power state in both of these D-states. 23 March 11, 2007 File: chalupsky_01_0307 Device Power States (cont.) D3 (Off): • D3 hot Primary power is not yet removed from the device. D3 hot maps to L1 to support clock removal on mobile platforms. PCI Bus clock is running. • D3 cold Primary power may

With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

These free resources are available to the Intel® Developer Network for PCI Express* Architecture community. PCI Express* Specifications. By downloading and reading these documents, you agree to the obligations set forth in the Intel® Developer Network for PCI Express* Architecture user agreement.

Introduction to PCI protocol Today’s computer systems, with their emphasis on high resolution graphics, full motion video, high bandwidth networking, and so on, go far beyond the capabilities of the architecture that ushered in the age of the personal computer in 1982.

Conventional PCI, often shortened to PCI, is a local computer bus for attaching hardware devices in a computer. PCI is the acronym for Peripheral Component Interconnect and is part of the PCI Local Bus …

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

Abstract – PCI (Peripheral Component Interconnect) is a computer bus for attaching hardware devices in a computer. Work on PCI first began at Intel’s Architecture Development Lab, circa 1990.

Amazon Web Services – Standardized Architecture for PCI DSS December 2016 Page 9 of 35 Amazon Glacier – Amazon Glacier is a storage service for archiving and long-term backup of infrequently used data. It provides secure, durable, and extremely low-cost storage, supports data transfer over SSL, and automatically encrypts data at rest. With Amazon Glacier, you can store your …

PCI-X, PCI-express to name a (relevant) few. All the bus types we will detail are vari- All the bus types we will detail are vari- ants of the PCI bus type, however some of …

• A data bus of 32-bits fetches, loads, or stores the instruction or data of 32-bits at one time Schaum’s Outline of Theory and Problems of Computer Architecture

PCI bus overview • PCI bus – Conventional PCI •Developed and standardised in early 90’s •32 or 64 bit shared parallel bus •Up to 66MHz (533MB/s) – PCI-X •Up to 133MHz (1066MB/s) – PCI Express •Consists of serial p2p links •Software-compatible with conventional PCI •Up to 16GB/s per device. PCI bus overview: memory space CPU RAM PCI controller Dev1 Dev3 Dev1 Dev2 Dev3 Dev2

Pcie tutorial pdf WordPress.com

What is Peripheral Component Interconnect Bus (PCI Bus

0 Bus Based Platforms.Obtaining PCI Bus Specifications. Chapter 2: Intro to PCI Bus Operation. Promotes PCI as an industry-wide standard. Transaction Completion and pamietnik ksiezniczki pdf Return of Bus to Idle State.als, because these days the PCI bus is the most

PCI bus provides a bus architecture that also supports peripherals and devices like Hard Disk Drives, Networks etc. PCI successfully replaced all other older buses like ISA, EISA and VL . PCI has various features. It is the only bus that can carry 64 bits of data in each clock cycle which makes it useful for Pentium processor family.

use the PCI testbench, you should have a basic understanding of PCI bus architecture and operations. f Refer to the PCI MegaCore Function User Guide for information on the

Conventional PCI, often shortened to PCI, is a local computer bus for attaching hardware devices in a computer. PCI is the acronym for Peripheral Component Interconnect and is part of the PCI Local Bus …

PCI architecture allows bus mastering of multiple devices on the bus simultaneously, with the arbitration circuitry working to ensure that no device on the bus …

DEVICE PROTOCOLS Lesson 22 PCI Bus PARALLEL BUS

438 PCI Architecture.ppt Arizona State University

With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

PCI bus overview • PCI bus – Conventional PCI •Developed and standardised in early 90’s •32 or 64 bit shared parallel bus •Up to 66MHz (533MB/s) – PCI-X •Up to 133MHz (1066MB/s) – PCI Express •Consists of serial p2p links •Software-compatible with conventional PCI •Up to 16GB/s per device. PCI bus overview: memory space CPU RAM PCI controller Dev1 Dev3 Dev1 Dev2 Dev3 Dev2

ISA (Industry Standard Architecture) — A transaction begins over the PCI bus — Each potential target on the bus decodes the transaction’s PCI address to determine whether it belongs to that target’s assigned address space – One target may be assigned a larger address space than another, and would thus respond to more addresses — The target that owns the PCI address then claims

• A data bus of 32-bits fetches, loads, or stores the instruction or data of 32-bits at one time Schaum’s Outline of Theory and Problems of Computer Architecture

*Some architectures also display the PCI domain information in the/proc/pci and/proc/bus/pci files. ,ch12.1659 Page 303 Friday, January 21, 2005 3:08 PM This is the Title of the Book, eMatter Edition

STANDARD I/O INTERFACES . The processor bus is the bus defied by the signals on the processor chip . itself. Devices that require a very high-speed connection to the processor, such as the

• PCI Power Management, USB, Cardbus, PCI Express, etc. • L1 state is the required link power state in both of these D-states. 23 March 11, 2007 File: chalupsky_01_0307 Device Power States (cont.) D3 (Off): • D3 hot Primary power is not yet removed from the device. D3 hot maps to L1 to support clock removal on mobile platforms. PCI Bus clock is running. • D3 cold Primary power may

Using PCI, a computer can support both new PCI cards while continuing to support Industry Standard Architecture expansion cards, an older standard. Designed by Intel, the original PCI was similar to the VESA Local Bus .

Based on existing PCI architecture ¾Conventional 33/66 MHz PCI adapters can be used in PCI-X slots ¾PCI-X adapters can be used in conventional PCI slots Provides two speed grades: 66 MHz and 133 MHz ¾The slowest board dictates the maximum speed on a particular bus ! Targeted at high-end data networking and storage network applications . February 2003 Page 9 PCI-X 2.0 Based on PCI-X …

Realistic PC architecture Advanced Programable Interrupt Controller bus I/O APIC CPU Bridge Main memory North bus side front-South Bridge bus ISA CPU USB bus AGP PCI

PCI bus provides a bus architecture that also supports peripherals and devices like Hard Disk Drives, Networks etc. PCI successfully replaced all other older buses like ISA, EISA and VL . PCI has various features. It is the only bus that can carry 64 bits of data in each clock cycle which makes it useful for Pentium processor family.

Refer to the following table for PCI bus architecture performance capabilities. A standard PCI bus can be up to four slots. Each slot can be any combination listed on the chart below. Electrical signaling is an important part of the PCI specification. The PCI signal is a “reflective” signal meaning that the signal travels to the end of the bus, and as the reflection travels back the other

PC-based instrumentation and microcontrollers Computer buses and interfaces the capacity of a desktop computer with a PCI/PCIe bus. • One of the most important benefits PXI offers is its integrated timing and triggering features. Without any external connections, multiple devices can be synchronized by using the internal buses resident on the backplane of a PXI chassis • By taking

For example, through the mechanical architecture, the system controller is defined to be in the leftmost slot of a PXI chassis to ensure it is at the left end of the PCI bus segment. It simplifies the integration and increases the degree of compatibility between chassis …

What is PCI Bus? Features of PCI Bus ~ Wiki For You

Memory and I/O buses Stanford University

information on bus architectures and bus protocols, and then provides specific information on various industry standard bus architectures from the past and the present, and their advantages and disadvantages. It also describes how different types of bus architectures are used simultaneously in different parts of a modern personal computer. 1. Introduction A typical computer system is …

2 • PCI Express Port Bus Driver Support for Linux per PCI Express Port. However, this solution would lack the ability to have each service built

Conventional PCI, often shortened to PCI, is a local computer bus for attaching hardware devices in a computer. PCI is the acronym for Peripheral Component Interconnect and is part of the PCI Local Bus …

Amazon Web Services – Standardized Architecture for PCI DSS December 2016 Page 9 of 35 Amazon Glacier – Amazon Glacier is a storage service for archiving and long-term backup of infrequently used data. It provides secure, durable, and extremely low-cost storage, supports data transfer over SSL, and automatically encrypts data at rest. With Amazon Glacier, you can store your …

architecture. Number of embedded devices in a computer system use PCI Three standards for the devices interfacing with the PC Peripheral Component Interconnect (PCI) Bus. 2008 Chapter-3 L22: “Embedded Systems – ” , Raj Kamal, Publs.: McGraw-Hill Education 13 PCI 32bit/33 MHz, and 64bit/66 MHz PCI Extended (PCI/X) 64 bit/100 MHz , Compact PCI (cPCI) Bus Two super speed versions PCI …

Eli Billauer The anatomy of a PCI/PCI Express kernel driver. Introduction Part I: The hardware The Strategy Part II: Code highlights Introduction Eli Billauer The anatomy of a PCI/PCI Express kernel driver. Introduction Part I: The hardware The Strategy Part II: Code highlights Overview Kernel programming is copying from people knowing better than you. Reading PCI/PCIe drivers is being told

Rev. 1.0 Sys MFG T/ED 4/25/2003 PC Architecture For Technicians Level-1 Technical Excellence Development Series Ch 14 – Page 7 Introduction lThe PCI Bus Solution

Introduction to PCI protocol Today’s computer systems, with their emphasis on high resolution graphics, full motion video, high bandwidth networking, and so on, go far beyond the capabilities of the architecture that ushered in the age of the personal computer in 1982.

Using PCI, a computer can support both new PCI cards while continuing to support Industry Standard Architecture expansion cards, an older standard. Designed by Intel, the original PCI was similar to the VESA Local Bus .

pci bus demystified second edition by doug abbott amsterdam • boston • heidelberg • london new york • oxford • paris • san diego san francisco • singapore • sydney • tokyo

PCI bus provides a bus architecture that also supports peripherals and devices like Hard Disk Drives, Networks etc. PCI successfully replaced all other older buses like ISA, EISA and VL . PCI has various features. It is the only bus that can carry 64 bits of data in each clock cycle which makes it useful for Pentium processor family.

Architecture Tutorial Alan Goodrum Chairman, PCI-X Workgroup Staff Fellow, Compaq Computer Corporation May 23, 2000 Applied Computing Conference 2000

Based on existing PCI architecture ¾Conventional 33/66 MHz PCI adapters can be used in PCI-X slots ¾PCI-X adapters can be used in conventional PCI slots Provides two speed grades: 66 MHz and 133 MHz ¾The slowest board dictates the maximum speed on a particular bus ! Targeted at high-end data networking and storage network applications . February 2003 Page 9 PCI-X 2.0 Based on PCI-X …

These free resources are available to the Intel® Developer Network for PCI Express* Architecture community. PCI Express* Specifications. By downloading and reading these documents, you agree to the obligations set forth in the Intel® Developer Network for PCI Express* Architecture user agreement.

Description : With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

Standardized Architecture for PCI DSS on the AWS Cloud

Introduction to the PXI Architecture National Instruments

0 Bus Based Platforms.Obtaining PCI Bus Specifications. Chapter 2: Intro to PCI Bus Operation. Promotes PCI as an industry-wide standard. Transaction Completion and pamietnik ksiezniczki pdf Return of Bus to Idle State.als, because these days the PCI bus is the most

Understanding PCI Bus, PCI-Express and In finiBand Architecture Contrasting The Architectures Mellanox Technologies Inc 2 Rev 1.20 slots. The following table highlights the key featur es that distinguish Infi niBand from simple local bus architectures such as PCI and PCI-Express: As can be seen from the table above, the InfiniBand architecture supports features that make it substantially …

*Some architectures also display the PCI domain information in the/proc/pci and/proc/bus/pci files. ,ch12.1659 Page 303 Friday, January 21, 2005 3:08 PM This is the Title of the Book, eMatter Edition

PCI architecture allows bus mastering of multiple devices on the bus simultaneously, with the arbitration circuitry working to ensure that no device on the bus …

Watchdog timer attached to PCI bus (part of the Intel i6300ESB chipset). Two cascaded, programmable timers (“stages”). When first stage times out, second stage …

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

Basic Bus Architecture Add-in Cards Processor Processor 56K 56K System Modem Modem ISA System MPEG MPEG Expansion Expansion Host Host 3D 3D Sound Sound Video Video Bus Bus Bridge Bridge Card Card Capture Capture Bridge Bridge Card Card PCI PCI Local Local Bus Bus 3

The PCI bus was introduced to the standard PC architecture in the early 90’s and has maintained its dominance with only one major upgrade during that period: from 32 bit/33 MHz to 64bit/66Mhz. The PCI-X initiative takes this one step further to 133MHz and seemingly should provide the PCI architecture with a few more years of life. But there is a divergence between what personal computers and

Pcie tutorial pdf Pcie tutorial pdf Pcie tutorial pdf DOWNLOAD! DIRECT DOWNLOAD! Pcie tutorial pdf Yet PCI Express architecture is significantly different from its predecessors PCI. 0 PHYs may optionally support 5 GTs signaling,

pci-pci-bus-numbering The Linux Documentation Project

Memory and I/O buses Stanford University

PCI architecture allows bus mastering of multiple devices on the bus simultaneously, with the arbitration circuitry working to ensure that no device on the bus …

These free resources are available to the Intel® Developer Network for PCI Express* Architecture community. PCI Express* Specifications. By downloading and reading these documents, you agree to the obligations set forth in the Intel® Developer Network for PCI Express* Architecture user agreement.

use the PCI testbench, you should have a basic understanding of PCI bus architecture and operations. f Refer to the PCI MegaCore Function User Guide for information on the

architecture. Number of embedded devices in a computer system use PCI Three standards for the devices interfacing with the PC Peripheral Component Interconnect (PCI) Bus. 2008 Chapter-3 L22: “Embedded Systems – ” , Raj Kamal, Publs.: McGraw-Hill Education 13 PCI 32bit/33 MHz, and 64bit/66 MHz PCI Extended (PCI/X) 64 bit/100 MHz , Compact PCI (cPCI) Bus Two super speed versions PCI …

Watchdog timer attached to PCI bus (part of the Intel i6300ESB chipset). Two cascaded, programmable timers (“stages”). When first stage times out, second stage …

PCI-X, PCI-express to name a (relevant) few. All the bus types we will detail are vari- All the bus types we will detail are vari- ants of the PCI bus type, however some of …

PCI bus ISA bus Socket-7 for processor South bridge North bridge Video adaptor DRAM IDE bus Video memory Level-2 cache

• PCI Power Management, USB, Cardbus, PCI Express, etc. • L1 state is the required link power state in both of these D-states. 23 March 11, 2007 File: chalupsky_01_0307 Device Power States (cont.) D3 (Off): • D3 hot Primary power is not yet removed from the device. D3 hot maps to L1 to support clock removal on mobile platforms. PCI Bus clock is running. • D3 cold Primary power may

Rev. 1.0 Sys MFG T/ED 4/25/2003 PC Architecture For Technicians Level-1 Technical Excellence Development Series Ch 14 – Page 7 Introduction lThe PCI Bus Solution

Abstract – PCI (Peripheral Component Interconnect) is a computer bus for attaching hardware devices in a computer. Work on PCI first began at Intel’s Architecture Development Lab, circa 1990.

PCI bus overview • PCI bus – Conventional PCI •Developed and standardised in early 90’s •32 or 64 bit shared parallel bus •Up to 66MHz (533MB/s) – PCI-X •Up to 133MHz (1066MB/s) – PCI Express •Consists of serial p2p links •Software-compatible with conventional PCI •Up to 16GB/s per device. PCI bus overview: memory space CPU RAM PCI controller Dev1 Dev3 Dev1 Dev2 Dev3 Dev2

Eli Billauer The anatomy of a PCI/PCI Express kernel driver. Introduction Part I: The hardware The Strategy Part II: Code highlights Introduction Eli Billauer The anatomy of a PCI/PCI Express kernel driver. Introduction Part I: The hardware The Strategy Part II: Code highlights Overview Kernel programming is copying from people knowing better than you. Reading PCI/PCIe drivers is being told

With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

Based on existing PCI architecture ¾Conventional 33/66 MHz PCI adapters can be used in PCI-X slots ¾PCI-X adapters can be used in conventional PCI slots Provides two speed grades: 66 MHz and 133 MHz ¾The slowest board dictates the maximum speed on a particular bus ! Targeted at high-end data networking and storage network applications . February 2003 Page 9 PCI-X 2.0 Based on PCI-X …

PCI Express Port Bus Driver Support for Linux

STANDARD I/O INTERFACES IDC-Online

9 PCI BUS • Introduced by Intel in 1992, PCI is short for Peripheral Component Interconnect and is a 32-bit computer bus that is also available as a 64-bit bus today.

PCI Bus Operation A guide for the uninformed by the slightly less uninformed! E. Hazen – 09/17/99 PCI Fundamentals The PCI bus is the de-facto standard bus for current-generation personal computers.

A Peripheral Component Interconnect Bus (PCI bus) connects the CPU and expansion boards such as modem cards, network cards and sound cards. These expansion boards are normally plugged into expansion slots on the motherboard.

Based on existing PCI architecture ¾Conventional 33/66 MHz PCI adapters can be used in PCI-X slots ¾PCI-X adapters can be used in conventional PCI slots Provides two speed grades: 66 MHz and 133 MHz ¾The slowest board dictates the maximum speed on a particular bus ! Targeted at high-end data networking and storage network applications . February 2003 Page 9 PCI-X 2.0 Based on PCI-X …

current PCI architecture serves the need. You can choose the modules that are the best fit for You can choose the modules that are the best fit for your applications, without being concerned whether they are using PCI or PCI Express signaling.

Refer to the following table for PCI bus architecture performance capabilities. A standard PCI bus can be up to four slots. Each slot can be any combination listed on the chart below. Electrical signaling is an important part of the PCI specification. The PCI signal is a “reflective” signal meaning that the signal travels to the end of the bus, and as the reflection travels back the other

PC-based instrumentation and microcontrollers Computer buses and interfaces the capacity of a desktop computer with a PCI/PCIe bus. • One of the most important benefits PXI offers is its integrated timing and triggering features. Without any external connections, multiple devices can be synchronized by using the internal buses resident on the backplane of a PXI chassis • By taking

Rev. 1.0 Sys MFG T/ED 4/25/2003 PC Architecture For Technicians Level-1 Technical Excellence Development Series Ch 14 – Page 7 Introduction lThe PCI Bus Solution

Abstract – PCI (Peripheral Component Interconnect) is a computer bus for attaching hardware devices in a computer. Work on PCI first began at Intel’s Architecture Development Lab, circa 1990.

PCI architecture allows bus mastering of multiple devices on the bus simultaneously, with the arbitration circuitry working to ensure that no device on the bus …

use the PCI testbench, you should have a basic understanding of PCI bus architecture and operations. f Refer to the PCI MegaCore Function User Guide for information on the

XPRESS PECIFICATION T pxisa.org

WISHBONE System-on-Chip (SoC) Interconnection Architecture

These free resources are available to the Intel® Developer Network for PCI Express* Architecture community. PCI Express* Specifications. By downloading and reading these documents, you agree to the obligations set forth in the Intel® Developer Network for PCI Express* Architecture user agreement.

26/03/2017 · In this video, we discuss the basics of PCI – Type0/1 headers and bus enumeration, so that we can easily transition to PCIe. Understanding of …

For example, through the mechanical architecture, the system controller is defined to be in the leftmost slot of a PXI chassis to ensure it is at the left end of the PCI bus segment. It simplifies the integration and increases the degree of compatibility between chassis …

9 PCI BUS • Introduced by Intel in 1992, PCI is short for Peripheral Component Interconnect and is a 32-bit computer bus that is also available as a 64-bit bus today.

use the PCI testbench, you should have a basic understanding of PCI bus architecture and operations. f Refer to the PCI MegaCore Function User Guide for information on the

information on bus architectures and bus protocols, and then provides specific information on various industry standard bus architectures from the past and the present, and their advantages and disadvantages. It also describes how different types of bus architectures are used simultaneously in different parts of a modern personal computer. 1. Introduction A typical computer system is …

The PCI bus was introduced to the standard PC architecture in the early 90’s and has maintained its dominance with only one major upgrade during that period: from 32 bit/33 MHz to 64bit/66Mhz. The PCI-X initiative takes this one step further to 133MHz and seemingly should provide the PCI architecture with a few more years of life. But there is a divergence between what personal computers and

Figure 16: Address translation from PCI-EXPRESS bus address to AMBA Address….. 27 Figure 17: PCI AMBA Advanced Microcontroller Bus Architecture – On-Chip Communication Bus APB Advanced Peripheral Bus – AMBA standard bus for Low-power peripherals ASB Advanced System Bus – AMBA standard bus for High-performance ATX Advanced Technology Extended – motherboard form …

Abstract – PCI (Peripheral Component Interconnect) is a computer bus for attaching hardware devices in a computer. Work on PCI first began at Intel’s Architecture Development Lab, circa 1990.

2 • PCI Express Port Bus Driver Support for Linux per PCI Express Port. However, this solution would lack the ability to have each service built

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

STANDARD I/O INTERFACES . The processor bus is the bus defied by the signals on the processor chip . itself. Devices that require a very high-speed connection to the processor, such as the

PCI Tutorial 1/31/00 vs 1 TU Clausthal

PCI Tutorial 1/31/00 vs 1 uml.edu

For example, through the mechanical architecture, the system controller is defined to be in the leftmost slot of a PXI chassis to ensure it is at the left end of the PCI bus segment. It simplifies the integration and increases the degree of compatibility between chassis …

PCI-X, PCI-express to name a (relevant) few. All the bus types we will detail are vari- All the bus types we will detail are vari- ants of the PCI bus type, however some of …

• A data bus of 32-bits fetches, loads, or stores the instruction or data of 32-bits at one time Schaum’s Outline of Theory and Problems of Computer Architecture

PC-based instrumentation and microcontrollers Computer buses and interfaces the capacity of a desktop computer with a PCI/PCIe bus. • One of the most important benefits PXI offers is its integrated timing and triggering features. Without any external connections, multiple devices can be synchronized by using the internal buses resident on the backplane of a PXI chassis • By taking

PCI Bus Operation A guide for the uninformed by the slightly less uninformed! E. Hazen – 09/17/99 PCI Fundamentals The PCI bus is the de-facto standard bus for current-generation personal computers.

With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

Amazon Web Services – Standardized Architecture for PCI DSS December 2016 Page 9 of 35 Amazon Glacier – Amazon Glacier is a storage service for archiving and long-term backup of infrequently used data. It provides secure, durable, and extremely low-cost storage, supports data transfer over SSL, and automatically encrypts data at rest. With Amazon Glacier, you can store your …

computer buses such as PCI bus and VMEbus. In fact, the WISHBONE architecture is analogous to a microcomputer bus in that that they both: (a) offer a flexible integration solution that can be easily tailored to a specific application; (b)

Refer to the following table for PCI bus architecture performance capabilities. A standard PCI bus can be up to four slots. Each slot can be any combination listed on the chart below. Electrical signaling is an important part of the PCI specification. The PCI signal is a “reflective” signal meaning that the signal travels to the end of the bus, and as the reflection travels back the other

Using PCI, a computer can support both new PCI cards while continuing to support Industry Standard Architecture expansion cards, an older standard. Designed by Intel, the original PCI was similar to the VESA Local Bus .

These free resources are available to the Intel® Developer Network for PCI Express* Architecture community. PCI Express* Specifications. By downloading and reading these documents, you agree to the obligations set forth in the Intel® Developer Network for PCI Express* Architecture user agreement.

13-slot PXI system can be built using a single PCI-PCI bridge. The PXI specification The PXI specification adds electrical features that meet the high-performance requirements of

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

current PCI architecture serves the need. You can choose the modules that are the best fit for You can choose the modules that are the best fit for your applications, without being concerned whether they are using PCI or PCI Express signaling.

Pcie tutorial pdf Pcie tutorial pdf Pcie tutorial pdf DOWNLOAD! DIRECT DOWNLOAD! Pcie tutorial pdf Yet PCI Express architecture is significantly different from its predecessors PCI. 0 PHYs may optionally support 5 GTs signaling,

Introduction to InfiniBand Mellanox Technologies

Standardized Architecture for PCI DSS on the AWS Cloud

Figure 16: Address translation from PCI-EXPRESS bus address to AMBA Address….. 27 Figure 17: PCI AMBA Advanced Microcontroller Bus Architecture – On-Chip Communication Bus APB Advanced Peripheral Bus – AMBA standard bus for Low-power peripherals ASB Advanced System Bus – AMBA standard bus for High-performance ATX Advanced Technology Extended – motherboard form …

Amazon Web Services – Standardized Architecture for PCI DSS December 2016 Page 9 of 35 Amazon Glacier – Amazon Glacier is a storage service for archiving and long-term backup of infrequently used data. It provides secure, durable, and extremely low-cost storage, supports data transfer over SSL, and automatically encrypts data at rest. With Amazon Glacier, you can store your …

Realistic PC architecture Advanced Programable Interrupt Controller bus I/O APIC CPU Bridge Main memory North bus side front-South Bridge bus ISA CPU USB bus AGP PCI

A Peripheral Component Interconnect Bus (PCI bus) connects the CPU and expansion boards such as modem cards, network cards and sound cards. These expansion boards are normally plugged into expansion slots on the motherboard.

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

2 • PCI Express Port Bus Driver Support for Linux per PCI Express Port. However, this solution would lack the ability to have each service built

• A data bus of 32-bits fetches, loads, or stores the instruction or data of 32-bits at one time Schaum’s Outline of Theory and Problems of Computer Architecture

9 PCI BUS • Introduced by Intel in 1992, PCI is short for Peripheral Component Interconnect and is a 32-bit computer bus that is also available as a 64-bit bus today.

0 Bus Based Platforms.Obtaining PCI Bus Specifications. Chapter 2: Intro to PCI Bus Operation. Promotes PCI as an industry-wide standard. Transaction Completion and pamietnik ksiezniczki pdf Return of Bus to Idle State.als, because these days the PCI bus is the most

current PCI architecture serves the need. You can choose the modules that are the best fit for You can choose the modules that are the best fit for your applications, without being concerned whether they are using PCI or PCI Express signaling.

The PCI bus was introduced to the standard PC architecture in the early 90’s and has maintained its dominance with only one major upgrade during that period: from 32 bit/33 MHz to 64bit/66Mhz. The PCI-X initiative takes this one step further to 133MHz and seemingly should provide the PCI architecture with a few more years of life. But there is a divergence between what personal computers and

PCI bus overview • PCI bus – Conventional PCI •Developed and standardised in early 90’s •32 or 64 bit shared parallel bus •Up to 66MHz (533MB/s) – PCI-X •Up to 133MHz (1066MB/s) – PCI Express •Consists of serial p2p links •Software-compatible with conventional PCI •Up to 16GB/s per device. PCI bus overview: memory space CPU RAM PCI controller Dev1 Dev3 Dev1 Dev2 Dev3 Dev2

What is PCI (Peripheral Component Interconnect

Implementing a PCI-Express AMBA interface controller on a

STANDARD I/O INTERFACES . The processor bus is the bus defied by the signals on the processor chip . itself. Devices that require a very high-speed connection to the processor, such as the

information on bus architectures and bus protocols, and then provides specific information on various industry standard bus architectures from the past and the present, and their advantages and disadvantages. It also describes how different types of bus architectures are used simultaneously in different parts of a modern personal computer. 1. Introduction A typical computer system is …

PCI Bus Operation A guide for the uninformed by the slightly less uninformed! E. Hazen – 09/17/99 PCI Fundamentals The PCI bus is the de-facto standard bus for current-generation personal computers.

26/03/2017 · In this video, we discuss the basics of PCI – Type0/1 headers and bus enumeration, so that we can easily transition to PCIe. Understanding of …

If the PCI device that was found was a PCI-PCI bridge then a pci_bus data structure is built and linked into the tree of pci_bus and pci_dev data structures pointed at by pci_root. The PCI initialisation code can tell if the PCI device is a PCI-PCI Bridge because it has a class code of 0x060400 .

0 Bus Based Platforms.Obtaining PCI Bus Specifications. Chapter 2: Intro to PCI Bus Operation. Promotes PCI as an industry-wide standard. Transaction Completion and pamietnik ksiezniczki pdf Return of Bus to Idle State.als, because these days the PCI bus is the most

PCI-X, PCI-express to name a (relevant) few. All the bus types we will detail are vari- All the bus types we will detail are vari- ants of the PCI bus type, however some of …

Based on existing PCI architecture ¾Conventional 33/66 MHz PCI adapters can be used in PCI-X slots ¾PCI-X adapters can be used in conventional PCI slots Provides two speed grades: 66 MHz and 133 MHz ¾The slowest board dictates the maximum speed on a particular bus ! Targeted at high-end data networking and storage network applications . February 2003 Page 9 PCI-X 2.0 Based on PCI-X …

WISHBONE System-on-Chip (SoC) Interconnection Architecture

pci-pci-bus-numbering The Linux Documentation Project

Watchdog timer attached to PCI bus (part of the Intel i6300ESB chipset). Two cascaded, programmable timers (“stages”). When first stage times out, second stage …

ISA (Industry Standard Architecture) — A transaction begins over the PCI bus — Each potential target on the bus decodes the transaction’s PCI address to determine whether it belongs to that target’s assigned address space – One target may be assigned a larger address space than another, and would thus respond to more addresses — The target that owns the PCI address then claims

Figure 16: Address translation from PCI-EXPRESS bus address to AMBA Address….. 27 Figure 17: PCI AMBA Advanced Microcontroller Bus Architecture – On-Chip Communication Bus APB Advanced Peripheral Bus – AMBA standard bus for Low-power peripherals ASB Advanced System Bus – AMBA standard bus for High-performance ATX Advanced Technology Extended – motherboard form …

Description : With 24,000 copies of the third edition sold worldwide, “PCI System Architecture” has established itself as an essential training tool for the PCI industry. This new fourth edition describes revision 2.2 of the Peripheral Component Interconnect (PCI) bus specification.

Understanding PCI Bus, PCI-Express and In finiBand Architecture Contrasting The Architectures Mellanox Technologies Inc 2 Rev 1.20 slots. The following table highlights the key featur es that distinguish Infi niBand from simple local bus architectures such as PCI and PCI-Express: As can be seen from the table above, the InfiniBand architecture supports features that make it substantially …

information on bus architectures and bus protocols, and then provides specific information on various industry standard bus architectures from the past and the present, and their advantages and disadvantages. It also describes how different types of bus architectures are used simultaneously in different parts of a modern personal computer. 1. Introduction A typical computer system is …

Pcie tutorial pdf Pcie tutorial pdf Pcie tutorial pdf DOWNLOAD! DIRECT DOWNLOAD! Pcie tutorial pdf Yet PCI Express architecture is significantly different from its predecessors PCI. 0 PHYs may optionally support 5 GTs signaling,

PCI bus provides a bus architecture that also supports peripherals and devices like Hard Disk Drives, Networks etc. PCI successfully replaced all other older buses like ISA, EISA and VL . PCI has various features. It is the only bus that can carry 64 bits of data in each clock cycle which makes it useful for Pentium processor family.

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

Based on existing PCI architecture ¾Conventional 33/66 MHz PCI adapters can be used in PCI-X slots ¾PCI-X adapters can be used in conventional PCI slots Provides two speed grades: 66 MHz and 133 MHz ¾The slowest board dictates the maximum speed on a particular bus ! Targeted at high-end data networking and storage network applications . February 2003 Page 9 PCI-X 2.0 Based on PCI-X …

Using PCI, a computer can support both new PCI cards while continuing to support Industry Standard Architecture expansion cards, an older standard. Designed by Intel, the original PCI was similar to the VESA Local Bus .

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

9 PCI BUS • Introduced by Intel in 1992, PCI is short for Peripheral Component Interconnect and is a 32-bit computer bus that is also available as a 64-bit bus today.

0 Bus Based Platforms.Obtaining PCI Bus Specifications. Chapter 2: Intro to PCI Bus Operation. Promotes PCI as an industry-wide standard. Transaction Completion and pamietnik ksiezniczki pdf Return of Bus to Idle State.als, because these days the PCI bus is the most

PCI Bus Operation Nevis Laboratories

Architecture Tutorial University of Northern Iowa

Chapter 14 PCI BUS Overview Chemeketa Community College

9 PCI BUS • Introduced by Intel in 1992, PCI is short for Peripheral Component Interconnect and is a 32-bit computer bus that is also available as a 64-bit bus today.

Computer Bus Architecture christie alwis

DEVICE PROTOCOLS Lesson 22 PCI Bus PARALLEL BUS

Rev. 1.0 Sys MFG T/ED 4/25/2003 PC Architecture For Technicians Level-1 Technical Excellence Development Series Ch 14 – Page 7 Introduction lThe PCI Bus Solution

Pcie tutorial pdf WordPress.com

COMP9242 2010/S2 Week 7

Rev. 1.0 Sys MFG T/ED 4/25/2003 PC Architecture For Technicians Level-1 Technical Excellence Development Series Ch 14 – Page 7 Introduction lThe PCI Bus Solution

Xilix Pci Tutorial Electronic Engineering Computer

pci bus demystified Download eBook pdf epub tuebl mobi

2 • PCI Express Port Bus Driver Support for Linux per PCI Express Port. However, this solution would lack the ability to have each service built

STANDARD I/O INTERFACES IDC-Online

PCI Bus Operation A guide for the uninformed by the slightly less uninformed! E. Hazen – 09/17/99 PCI Fundamentals The PCI bus is the de-facto standard bus for current-generation personal computers.

Introduction to InfiniBand Mellanox Technologies

CHAPTER 12 PCI Drivers LWN.net

PCI Tutorial 1/31/00 vs 1 TU Clausthal

• A data bus of 32-bits fetches, loads, or stores the instruction or data of 32-bits at one time Schaum’s Outline of Theory and Problems of Computer Architecture

STANDARD I/O INTERFACES IDC-Online

DEVICE PROTOCOLS Lesson 22 PCI Bus PARALLEL BUS

PCI bus ISA bus Socket-7 for processor South bridge North bridge Video adaptor DRAM IDE bus Video memory Level-2 cache

PCI Tutorial 1/31/00 vs 1 uml.edu

Implementing a PCI-Express AMBA interface controller on a

information on bus architectures and bus protocols, and then provides specific information on various industry standard bus architectures from the past and the present, and their advantages and disadvantages. It also describes how different types of bus architectures are used simultaneously in different parts of a modern personal computer. 1. Introduction A typical computer system is …

Computer Bus Architecture christie alwis

XPRESS PECIFICATION T pxisa.org

PCI Bus Demystified pudn.com

use the PCI testbench, you should have a basic understanding of PCI bus architecture and operations. f Refer to the PCI MegaCore Function User Guide for information on the

PCI Testbench User Guide intel.com

Bus Stru computer organization Part 3Functional units and

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

Xilix Pci Tutorial Electronic Engineering Computer

Chapter 14 PCI BUS Overview Chemeketa Community College

STANDARD I/O INTERFACES . The processor bus is the bus defied by the signals on the processor chip . itself. Devices that require a very high-speed connection to the processor, such as the

Bus Architectures EOLSS

• PCI Power Management, USB, Cardbus, PCI Express, etc. • L1 state is the required link power state in both of these D-states. 23 March 11, 2007 File: chalupsky_01_0307 Device Power States (cont.) D3 (Off): • D3 hot Primary power is not yet removed from the device. D3 hot maps to L1 to support clock removal on mobile platforms. PCI Bus clock is running. • D3 cold Primary power may

Epics Driver/Device Support Tutorial Stanford University

These free resources are available to the Intel® Developer Network for PCI Express* Architecture community. PCI Express* Specifications. By downloading and reading these documents, you agree to the obligations set forth in the Intel® Developer Network for PCI Express* Architecture user agreement.

Epics Driver/Device Support Tutorial Stanford University

Introduction to the PXI Architecture National Instruments

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

Xilix Pci Tutorial Electronic Engineering Computer

438 PCI Architecture.ppt Arizona State University

information on bus architectures and bus protocols, and then provides specific information on various industry standard bus architectures from the past and the present, and their advantages and disadvantages. It also describes how different types of bus architectures are used simultaneously in different parts of a modern personal computer. 1. Introduction A typical computer system is …

COMP9242 2010/S2 Week 7

CHAPTER 12 PCI Drivers LWN.net

The History of the PCI Bus Architecture NComm

13-slot PXI system can be built using a single PCI-PCI bridge. The PXI specification The PXI specification adds electrical features that meet the high-performance requirements of

Chapter 14 PCI BUS Overview Chemeketa Community College

PCI uses a shared bus topology to allow for communication among the different devices on the bus; the different PCI devices (i.e., a network card, a sound card, a RAID card, etc.) are all attached to the same bus, which they use to communicate with the CPU. Take a look at the following diagram to get a feel for what a shared bus looks like.

PCI Tutorial 1/31/00 vs 1 uml.edu

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

Introduction to the PXI Architecture National Instruments

Pcie tutorial pdf WordPress.com

Pci bus tutorial pdf WordPress.com

Watchdog timer attached to PCI bus (part of the Intel i6300ESB chipset). Two cascaded, programmable timers (“stages”). When first stage times out, second stage …

Epics Driver/Device Support Tutorial Stanford University

Peripheral Component Interconnect (PCI) bus

PCI Bus Operation Nevis Laboratories

PCI Bus Operation A guide for the uninformed by the slightly less uninformed! E. Hazen – 09/17/99 PCI Fundamentals The PCI bus is the de-facto standard bus for current-generation personal computers.

PCI Bus Operation Nevis Laboratories

PCI Tutorial 1/31/00 vs 1 TU Clausthal

A Peripheral Component Interconnect Bus (PCI bus) connects the CPU and expansion boards such as modem cards, network cards and sound cards. These expansion boards are normally plugged into expansion slots on the motherboard.

438 PCI Architecture.ppt Arizona State University

Standardized Architecture for PCI DSS on the AWS Cloud

PCI bus ISA bus Socket-7 for processor South bridge North bridge Video adaptor DRAM IDE bus Video memory Level-2 cache

PC Architecture Napier

Realistic PC architecture Advanced Programable Interrupt Controller bus I/O APIC CPU Bridge Main memory North bus side front-South Bridge bus ISA CPU USB bus AGP PCI

Implementing a PCI-Express AMBA interface controller on a

The History of the PCI Bus Architecture NComm

XPRESS PECIFICATION T pxisa.org

information on bus architectures and bus protocols, and then provides specific information on various industry standard bus architectures from the past and the present, and their advantages and disadvantages. It also describes how different types of bus architectures are used simultaneously in different parts of a modern personal computer. 1. Introduction A typical computer system is …

pci bus demystified Download eBook pdf epub tuebl mobi

• PCI Power Management, USB, Cardbus, PCI Express, etc. • L1 state is the required link power state in both of these D-states. 23 March 11, 2007 File: chalupsky_01_0307 Device Power States (cont.) D3 (Off): • D3 hot Primary power is not yet removed from the device. D3 hot maps to L1 to support clock removal on mobile platforms. PCI Bus clock is running. • D3 cold Primary power may

Memory and I/O buses Stanford University

Computer Bus Architecture christie alwis

Pci bus tutorial pdf WordPress.com

0 Bus Based Platforms.Obtaining PCI Bus Specifications. Chapter 2: Intro to PCI Bus Operation. Promotes PCI as an industry-wide standard. Transaction Completion and pamietnik ksiezniczki pdf Return of Bus to Idle State.als, because these days the PCI bus is the most

PCI Tutorial Electronics Physical Layer Protocols

Watchdog timer attached to PCI bus (part of the Intel i6300ESB chipset). Two cascaded, programmable timers (“stages”). When first stage times out, second stage …

WISHBONE System-on-Chip (SoC) Interconnection Architecture

Inc.Basic Bus Architecture Add-in Cards Processor Processor System System 56K 56K Modem Modem ISA Host Host Bridge Bridge Expansion Expansion Bus Bus Bridge Bridge 3D Sound 3D Sound Card Card MPEG MPEG Video Video Capture Capture Card Card PCI Local Bus PCI Local Bus 3D 3D Graphics Graphics Card Card SCSI SCSI Controller Controller 100 Mbit 100 Mbit Ethernet Ethernet Motherboard LAN PCI …

Bus Architectures EOLSS

26/03/2017 · In this video, we discuss the basics of PCI – Type0/1 headers and bus enumeration, so that we can easily transition to PCIe. Understanding of …

The History of the PCI Bus Architecture NComm

Introduction to PCI protocol electrofriends.com

architecture. Number of embedded devices in a computer system use PCI Three standards for the devices interfacing with the PC Peripheral Component Interconnect (PCI) Bus. 2008 Chapter-3 L22: “Embedded Systems – ” , Raj Kamal, Publs.: McGraw-Hill Education 13 PCI 32bit/33 MHz, and 64bit/66 MHz PCI Extended (PCI/X) 64 bit/100 MHz , Compact PCI (cPCI) Bus Two super speed versions PCI …

COMP9242 2010/S2 Week 7

438 PCI Architecture.ppt Arizona State University

STANDARD I/O INTERFACES . The processor bus is the bus defied by the signals on the processor chip . itself. Devices that require a very high-speed connection to the processor, such as the

System Architecture 6 PCI Basics and Bus Enumeration

PCI uses a shared bus topology to allow for communication among the different devices on the bus; the different PCI devices (i.e., a network card, a sound card, a RAID card, etc.) are all attached to the same bus, which they use to communicate with the CPU. Take a look at the following diagram to get a feel for what a shared bus looks like.

Epics Driver/Device Support Tutorial Stanford University

Chapter 14 PCI BUS Overview Chemeketa Community College

Amazon Web Services – Standardized Architecture for PCI DSS December 2016 Page 9 of 35 Amazon Glacier – Amazon Glacier is a storage service for archiving and long-term backup of infrequently used data. It provides secure, durable, and extremely low-cost storage, supports data transfer over SSL, and automatically encrypts data at rest. With Amazon Glacier, you can store your …

PXI Specification PCI eXtensions for Instrumentation

PCI Tutorial 1/31/00 vs 1 uml.edu

PCI architecture allows bus mastering of multiple devices on the bus simultaneously, with the arbitration circuitry working to ensure that no device on the bus …

PCI Tutorial 1/31/00 vs 1 TU Clausthal

Bus Architectures EOLSS

Pci bus tutorial pdf WordPress.com

Conventional PCI, often shortened to PCI, is a local computer bus for attaching hardware devices in a computer. PCI is the acronym for Peripheral Component Interconnect and is part of the PCI Local Bus …

PCI Bus Demystified pudn.com

Introduction to PCI protocol Today’s computer systems, with their emphasis on high resolution graphics, full motion video, high bandwidth networking, and so on, go far beyond the capabilities of the architecture that ushered in the age of the personal computer in 1982.

PC Architecture Napier

13-slot PXI system can be built using a single PCI-PCI bridge. The PXI specification The PXI specification adds electrical features that meet the high-performance requirements of

PCI Tutorial 1/31/00 vs 1 TU Clausthal

Download pci bus demystified or read online books in PDF, EPUB, Tuebl, and Mobi Format. Click Download or Read Online button to get pci bus demystified book now. This site is like a library, Use search box in the widget to get ebook that you want.

System Architecture 6 PCI Basics and Bus Enumeration

http://WWW.TESTBENCH.IN