Pci express 4.0 specification pdf

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification’s previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

2017 Microchip Technology Inc. DS00002484A-page 5 AN2484 Note 1: Jitter specification for PCIe 4.0 is <500 fsRMS. All values in the table are fsRMS.

6 PCIe Express* (PCIe*) 4.0 Retimer Supplemental Features and Standard BGA Footprint June 2018 1 Introduction 1.1 Overview PCI Express* (PCIe*) 4.0 capable retimers extend the …

Description: Different Receiver Architectures: PCI Express 3.0 add-in Card RX CEM is only required to work at E-12 at one point of choosing with the reference spec channel (~ 20 dB).

GRL-PCIE4-BASE-RXA is used for testing your PCIe® 4.0 Receiver to the Base (ASIC) Specification, while GRL-PCIE4-CEM-RXA is used for testing end products to the PCIe® 4.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE4-RXA provides a simple user interface to automate complex PCIe testing. The software runs on Windows 7 or higher oscilloscope or any PC OS, and significantly …

The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to be shared with device vendors.

Compliant with PCIe 4.0, 3.0, 2.1, and 1.1 specifications, the Controller IP has over 100 configuration features to customize the controller to the specific needs of any

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

High-Speed Serial Bus Interface Solution for PCI Express, Thunderbolt, USB Signal Quality Analyzer MP1800A Series . 2 • Traffic volumes at data centers are exploding due to the spread of cloud computing services. Consequently, faster interfaces such as 100 GbE, 400 GbE, InfiniBand EDR, etc., are being deployed for communications between the servers and network equipment, while on the …

You might already know that PCI Express 4.0 is on its way. Back at the PCI-SIG’s (Special Interest Group) DevCon event in June, it was announced that the standard was complete and undergoing review.

The PCI Express® (PCIe®) standard has long been used in applications like personal computers, networking and workstations. Due to its many benefits such as reliability, low-power, latency and scalable bandwidth from 2.5 GT/s to 16 GT/s, the specification has evolved to also become prevalent in designs for storage, cloud computing, mobile and

PCIe 4.0 will arrive in 2017 with double the bandwidth, but it will also boost the amount of power provided at the slot up to a minimum of 300W, which might eliminate the need for auxiliary power

This specification describes the PCI Express archite… view more This specification describes the PCI Express architecture, interconnect attributes, fabric management, and the programming interface required to design and build systems and peripherals that are compliant with the PCI Express specification.

Now the PCI-SIG has announced that PCIe 4.0 specification is finished, and it plans to have PCIe 5.0 ready to go by 2019, which is liable to cripple the 4.0 spec before it even gets out of the gate.

“The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations,

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification. Download PDF for more information

The preceding PCIe 4.0 specification is designed with key functional enhancements that future-proof the PCIe architecture design, thereby accelerating speech and future design specifcations future

PCIe 3.1 and 4.0 Specifications Revealed Ryan Martin / 6 years ago Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s Hardware .

For the Tektronix BERTScope BSA and Real-Time Oscilloscope

/https/cip/skoob.s3.amazonaws.com/livros/33526/HITLER_E_AS_RELIGIOES_DA_SUASTICA_1246131638B.jpg)

PCIe 4.0 specification released MyBroadband

The Cadence® SpeedBridge® Adapter for PCI Express® (PCIe®) 4.0 provides efficient driver and application-level testing for verifying emulated PCIe 4.0 designs with the actual ASIC/SoC software/ hardware, driver development, and application development.

PCI-Express 4.0 has modified the filter scenarios for 2.5 G and 5 G, bringing them in alignment with the minimum 0.01 dB peaking seen in the 8 G and 16 G specifications. AN946: PCI-Express 4.0 …

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

SPECIFICATIONS PCIe-6738 PCI Express, 16-Bit, 32-Channel, 1 MS/s Analog Output Device Definitions Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty. Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty. • …

The multi-channel DesignWare® PHY IP for PCI Express® 4.0 includes Synopsys’ high-speed, high-performance transceiver to meet today’s applications’ demands for higher bandwidth. The PHY provides a cost-effective solution that is designed to meet the needs of today’s high-speed chip-to-chip

Quickly test your Receiver Design to the PCIe 4.0 Base Specification Description. GRL’s PCI Express®4.0 Base Specification Receiver Calibration and Test Automation Software for the Anritsu MP1800A BERT (GRL-PCIE4-BASE-RXA) provides an automated, simple, and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

As of now, the PCI Express 4.0 standard has been finalized and officially released. The new protocol promises twice the per-lane bandwidth of PCI Express 3.0, allowing a GPU or other accelerator

PCI-SIG members are welcome to access the PCIe 4.0 spec online at no cost through the PCI-SIG Specification Library. Non-members may purchase the specification here. PCIe 4.0 is a significant milestone, but we’re not resting.

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s.

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

the specification was first released, largely due to its software compatibility with PCI, which had already permeated the embedded world. PCIe offers low cost, high performance and flexibility, and since embedded systems are largely built with the same components used in other, higher-volume markets, PCIe is an ideal way to con-nect together the components inside embedded systems. As with most

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

The PCIe 4.0 specification was announced in June, and has now been published. PCIe 4.0’s major improvement over the previous specification is a maximum data rate of 16GT/s, as opposed to PCIe …

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

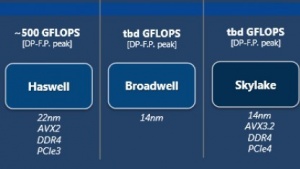

26/08/2016 · PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 / PCI Express GENERATION COMPARISON – Everything you need to know CHANNEL MAIN TEST RIG setup as following: Intel i9-9900K Processor purchase link

One is the official launch of the PCIe 4.0 specification that will take the baton from PCIe 3.0, and the other is early work on the standards eventual replacement, PCIe 5.0.

The PCIe 4.0 specification is available free of charge to PCI-SIG member companies via the official website, though non-members wishing to dive down into the nitty-gritty will be disappointed to

Software Version 4.0.0.1007 . Intel® Solid-State Drive PCIe* Driver July 2018 Release Notes 331995-006US 2 Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. Intel reserves these for future definition and shall have no

PCI Express* Gen4 Retimer Supplemental Features and Standard

– manual driving lessons sydney inner west

PCI Express* Gen4 Retimer Supplemental Features intel.in

PCI-SIG releases final specifications of PCIe 4.0 which

PCI Express 4.0 Draft 0.7 & PIPE 4.4 Specifications What

PCI Express 4.0 Technology Updates for Server and

Microchip’s Clock Devices’ Compliance with PCIe 4

Controller IP for PCIe 4

Intel® Solid State Drive Datacenter PCIe* Microsoft

https://fr.wikipedia.org/wiki/PCI_Express

High-Speed Serial Bus Interface Solution for PCI Express

– PCI-SIG Releases PCIe 4.0 Version 1.0 ServeTheHome

PCI SIG Releases PCI-Express Gen 4.0 Specifications

DesignWare PHY IP for PCI Express 4.0 Synopsys

DesignWare IP for PCI Express 4.0 Draft 0.7 Synopsys

PCI-SIG releases final specifications of PCIe 4.0 which

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

GRL-PCIE4-BASE-RXA is used for testing your PCIe® 4.0 Receiver to the Base (ASIC) Specification, while GRL-PCIE4-CEM-RXA is used for testing end products to the PCIe® 4.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE4-RXA provides a simple user interface to automate complex PCIe testing. The software runs on Windows 7 or higher oscilloscope or any PC OS, and significantly …

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

2017 Microchip Technology Inc. DS00002484A-page 5 AN2484 Note 1: Jitter specification for PCIe 4.0 is <500 fsRMS. All values in the table are fsRMS.

The multi-channel DesignWare® PHY IP for PCI Express® 4.0 includes Synopsys’ high-speed, high-performance transceiver to meet today’s applications’ demands for higher bandwidth. The PHY provides a cost-effective solution that is designed to meet the needs of today’s high-speed chip-to-chip

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

The PCI Express® (PCIe®) standard has long been used in applications like personal computers, networking and workstations. Due to its many benefits such as reliability, low-power, latency and scalable bandwidth from 2.5 GT/s to 16 GT/s, the specification has evolved to also become prevalent in designs for storage, cloud computing, mobile and

One is the official launch of the PCIe 4.0 specification that will take the baton from PCIe 3.0, and the other is early work on the standards eventual replacement, PCIe 5.0.

As of now, the PCI Express 4.0 standard has been finalized and officially released. The new protocol promises twice the per-lane bandwidth of PCI Express 3.0, allowing a GPU or other accelerator

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification's previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

Quickly test your Receiver Design to the PCIe 4.0 Base Specification Description. GRL’s PCI Express®4.0 Base Specification Receiver Calibration and Test Automation Software for the Anritsu MP1800A BERT (GRL-PCIE4-BASE-RXA) provides an automated, simple, and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

SPECIFICATIONS PCIe-6738 PCI Express, 16-Bit, 32-Channel, 1 MS/s Analog Output Device Definitions Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty. Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty. • …

PCIe 5.0 Arriving in 2019 With 4x More ExtremeTech

PCI-SIG releases final specifications of PCIe 4.0 which

PCIe 4.0 will arrive in 2017 with double the bandwidth, but it will also boost the amount of power provided at the slot up to a minimum of 300W, which might eliminate the need for auxiliary power

One is the official launch of the PCIe 4.0 specification that will take the baton from PCIe 3.0, and the other is early work on the standards eventual replacement, PCIe 5.0.

This specification describes the PCI Express archite… view more This specification describes the PCI Express architecture, interconnect attributes, fabric management, and the programming interface required to design and build systems and peripherals that are compliant with the PCI Express specification.

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

The preceding PCIe 4.0 specification is designed with key functional enhancements that future-proof the PCIe architecture design, thereby accelerating speech and future design specifcations future

26/08/2016 · PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 / PCI Express GENERATION COMPARISON – Everything you need to know CHANNEL MAIN TEST RIG setup as following: Intel i9-9900K Processor purchase link

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

High-Speed Serial Bus Interface Solution for PCI Express, Thunderbolt, USB Signal Quality Analyzer MP1800A Series . 2 • Traffic volumes at data centers are exploding due to the spread of cloud computing services. Consequently, faster interfaces such as 100 GbE, 400 GbE, InfiniBand EDR, etc., are being deployed for communications between the servers and network equipment, while on the …

PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s.

The PCI Express® (PCIe®) standard has long been used in applications like personal computers, networking and workstations. Due to its many benefits such as reliability, low-power, latency and scalable bandwidth from 2.5 GT/s to 16 GT/s, the specification has evolved to also become prevalent in designs for storage, cloud computing, mobile and

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

PCI-SIG members are welcome to access the PCIe 4.0 spec online at no cost through the PCI-SIG Specification Library. Non-members may purchase the specification here. PCIe 4.0 is a significant milestone, but we’re not resting.

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

Now the PCI-SIG has announced that PCIe 4.0 specification is finished, and it plans to have PCIe 5.0 ready to go by 2019, which is liable to cripple the 4.0 spec before it even gets out of the gate.

PCI Express* Gen4 Retimer Supplemental Features intel.in

PCI-SIG releases final specifications of PCIe 4.0 which

PCIe 3.1 and 4.0 Specifications Revealed Ryan Martin / 6 years ago Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s Hardware .

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification. Download PDF for more information

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

The PCIe 4.0 specification was announced in June, and has now been published. PCIe 4.0’s major improvement over the previous specification is a maximum data rate of 16GT/s, as opposed to PCIe …

PCI-SIG Releases PCIe 4.0 Version 1.0 ServeTheHome

Microchip’s Clock Devices’ Compliance with PCIe 4

PCIe 3.1 and 4.0 Specifications Revealed Ryan Martin / 6 years ago Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s Hardware .

Compliant with PCIe 4.0, 3.0, 2.1, and 1.1 specifications, the Controller IP has over 100 configuration features to customize the controller to the specific needs of any

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

You might already know that PCI Express 4.0 is on its way. Back at the PCI-SIG’s (Special Interest Group) DevCon event in June, it was announced that the standard was complete and undergoing review.

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification’s previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

Description: Different Receiver Architectures: PCI Express 3.0 add-in Card RX CEM is only required to work at E-12 at one point of choosing with the reference spec channel (~ 20 dB).

The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to be shared with device vendors.

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

Now the PCI-SIG has announced that PCIe 4.0 specification is finished, and it plans to have PCIe 5.0 ready to go by 2019, which is liable to cripple the 4.0 spec before it even gets out of the gate.

PCIe 4.0 will arrive in 2017 with double the bandwidth, but it will also boost the amount of power provided at the slot up to a minimum of 300W, which might eliminate the need for auxiliary power

PCIe 4.0 specification released MyBroadband

Microchip’s Clock Devices’ Compliance with PCIe 4

Description: Different Receiver Architectures: PCI Express 3.0 add-in Card RX CEM is only required to work at E-12 at one point of choosing with the reference spec channel (~ 20 dB).

PCI-SIG members are welcome to access the PCIe 4.0 spec online at no cost through the PCI-SIG Specification Library. Non-members may purchase the specification here. PCIe 4.0 is a significant milestone, but we’re not resting.

You might already know that PCI Express 4.0 is on its way. Back at the PCI-SIG’s (Special Interest Group) DevCon event in June, it was announced that the standard was complete and undergoing review.

One is the official launch of the PCIe 4.0 specification that will take the baton from PCIe 3.0, and the other is early work on the standards eventual replacement, PCIe 5.0.

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification. Download PDF for more information

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

This specification describes the PCI Express archite… view more This specification describes the PCI Express architecture, interconnect attributes, fabric management, and the programming interface required to design and build systems and peripherals that are compliant with the PCI Express specification.

The Cadence® SpeedBridge® Adapter for PCI Express® (PCIe®) 4.0 provides efficient driver and application-level testing for verifying emulated PCIe 4.0 designs with the actual ASIC/SoC software/ hardware, driver development, and application development.

The multi-channel DesignWare® PHY IP for PCI Express® 4.0 includes Synopsys’ high-speed, high-performance transceiver to meet today’s applications’ demands for higher bandwidth. The PHY provides a cost-effective solution that is designed to meet the needs of today’s high-speed chip-to-chip

GRL-PCIE4-BASE-RXA is used for testing your PCIe® 4.0 Receiver to the Base (ASIC) Specification, while GRL-PCIE4-CEM-RXA is used for testing end products to the PCIe® 4.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE4-RXA provides a simple user interface to automate complex PCIe testing. The software runs on Windows 7 or higher oscilloscope or any PC OS, and significantly …

“The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations,

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

the specification was first released, largely due to its software compatibility with PCI, which had already permeated the embedded world. PCIe offers low cost, high performance and flexibility, and since embedded systems are largely built with the same components used in other, higher-volume markets, PCIe is an ideal way to con-nect together the components inside embedded systems. As with most

PCI Express® 4.0 Base Specification Receiver Test

Intel® Solid State Drive Datacenter PCIe* Microsoft

PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s.

The preceding PCIe 4.0 specification is designed with key functional enhancements that future-proof the PCIe architecture design, thereby accelerating speech and future design specifcations future

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

You might already know that PCI Express 4.0 is on its way. Back at the PCI-SIG’s (Special Interest Group) DevCon event in June, it was announced that the standard was complete and undergoing review.

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

PCIe 3.1 and 4.0 Specifications Revealed Ryan Martin / 6 years ago Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s Hardware .

“The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations,

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

6 PCIe Express* (PCIe*) 4.0 Retimer Supplemental Features and Standard BGA Footprint June 2018 1 Introduction 1.1 Overview PCI Express* (PCIe*) 4.0 capable retimers extend the …

Now the PCI-SIG has announced that PCIe 4.0 specification is finished, and it plans to have PCIe 5.0 ready to go by 2019, which is liable to cripple the 4.0 spec before it even gets out of the gate.

PCI-SIG members are welcome to access the PCIe 4.0 spec online at no cost through the PCI-SIG Specification Library. Non-members may purchase the specification here. PCIe 4.0 is a significant milestone, but we’re not resting.

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

The PCI Express® (PCIe®) standard has long been used in applications like personal computers, networking and workstations. Due to its many benefits such as reliability, low-power, latency and scalable bandwidth from 2.5 GT/s to 16 GT/s, the specification has evolved to also become prevalent in designs for storage, cloud computing, mobile and

Quickly test your Receiver Design to the PCIe 4.0 Base Specification Description. GRL’s PCI Express®4.0 Base Specification Receiver Calibration and Test Automation Software for the Anritsu MP1800A BERT (GRL-PCIE4-BASE-RXA) provides an automated, simple, and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

SpeedBridge Adapter for PCIe 4 Cadence Design Systems

PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 youtube.com

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

You might already know that PCI Express 4.0 is on its way. Back at the PCI-SIG’s (Special Interest Group) DevCon event in June, it was announced that the standard was complete and undergoing review.

PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s.

Description: Different Receiver Architectures: PCI Express 3.0 add-in Card RX CEM is only required to work at E-12 at one point of choosing with the reference spec channel (~ 20 dB).

PCI Express* Gen4 Retimer Supplemental Features and Standard

PCI-SIG releases final specifications of PCIe 4.0 which

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification. Download PDF for more information

PCIe 3.1 and 4.0 Specifications Revealed Ryan Martin / 6 years ago Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s Hardware .

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

Software Version 4.0.0.1007 . Intel® Solid-State Drive PCIe* Driver July 2018 Release Notes 331995-006US 2 Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. Intel reserves these for future definition and shall have no

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

Compliant with PCIe 4.0, 3.0, 2.1, and 1.1 specifications, the Controller IP has over 100 configuration features to customize the controller to the specific needs of any

2017 Microchip Technology Inc. DS00002484A-page 5 AN2484 Note 1: Jitter specification for PCIe 4.0 is <500 fsRMS. All values in the table are fsRMS.

PCI Express 4.0 Technology Updates for Server and

PCI-SIG finalises PCIe 4.0 specification teases early

PCI-SIG members are welcome to access the PCIe 4.0 spec online at no cost through the PCI-SIG Specification Library. Non-members may purchase the specification here. PCIe 4.0 is a significant milestone, but we’re not resting.

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification’s previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

SpeedBridge Adapter for PCIe 4 Cadence Design Systems

PCI Express* Gen4 Retimer Supplemental Features intel.in

Now the PCI-SIG has announced that PCIe 4.0 specification is finished, and it plans to have PCIe 5.0 ready to go by 2019, which is liable to cripple the 4.0 spec before it even gets out of the gate.

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

The multi-channel DesignWare® PHY IP for PCI Express® 4.0 includes Synopsys’ high-speed, high-performance transceiver to meet today’s applications’ demands for higher bandwidth. The PHY provides a cost-effective solution that is designed to meet the needs of today’s high-speed chip-to-chip

The PCI Express® (PCIe®) standard has long been used in applications like personal computers, networking and workstations. Due to its many benefits such as reliability, low-power, latency and scalable bandwidth from 2.5 GT/s to 16 GT/s, the specification has evolved to also become prevalent in designs for storage, cloud computing, mobile and

GRL-PCIE4-BASE-RXA is used for testing your PCIe® 4.0 Receiver to the Base (ASIC) Specification, while GRL-PCIE4-CEM-RXA is used for testing end products to the PCIe® 4.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE4-RXA provides a simple user interface to automate complex PCIe testing. The software runs on Windows 7 or higher oscilloscope or any PC OS, and significantly …

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

PCIe 4.0 will arrive in 2017 with double the bandwidth, but it will also boost the amount of power provided at the slot up to a minimum of 300W, which might eliminate the need for auxiliary power

26/08/2016 · PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 / PCI Express GENERATION COMPARISON – Everything you need to know CHANNEL MAIN TEST RIG setup as following: Intel i9-9900K Processor purchase link

This specification describes the PCI Express archite… view more This specification describes the PCI Express architecture, interconnect attributes, fabric management, and the programming interface required to design and build systems and peripherals that are compliant with the PCI Express specification.

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification’s previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification. Download PDF for more information

Intel® Solid State Drive Datacenter PCIe* Microsoft

PCIe 4.0 specification released MyBroadband

PCI-Express 4.0 has modified the filter scenarios for 2.5 G and 5 G, bringing them in alignment with the minimum 0.01 dB peaking seen in the 8 G and 16 G specifications. AN946: PCI-Express 4.0 …

The PCI Express® (PCIe®) standard has long been used in applications like personal computers, networking and workstations. Due to its many benefits such as reliability, low-power, latency and scalable bandwidth from 2.5 GT/s to 16 GT/s, the specification has evolved to also become prevalent in designs for storage, cloud computing, mobile and

The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to be shared with device vendors.

Compliant with PCIe 4.0, 3.0, 2.1, and 1.1 specifications, the Controller IP has over 100 configuration features to customize the controller to the specific needs of any

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

As of now, the PCI Express 4.0 standard has been finalized and officially released. The new protocol promises twice the per-lane bandwidth of PCI Express 3.0, allowing a GPU or other accelerator

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

DesignWare PHY IP for PCI Express 4.0 Synopsys

PCIe 4 specifications arrive PC Perspective

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

This specification describes the PCI Express archite… view more This specification describes the PCI Express architecture, interconnect attributes, fabric management, and the programming interface required to design and build systems and peripherals that are compliant with the PCI Express specification.

Software Version 4.0.0.1007 . Intel® Solid-State Drive PCIe* Driver July 2018 Release Notes 331995-006US 2 Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. Intel reserves these for future definition and shall have no

SPECIFICATIONS PCIe-6738 PCI Express, 16-Bit, 32-Channel, 1 MS/s Analog Output Device Definitions Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty. Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty. • …

The PCIe 4.0 specification was announced in June, and has now been published. PCIe 4.0’s major improvement over the previous specification is a maximum data rate of 16GT/s, as opposed to PCIe …

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

Fore! PCI Express 4.0 finally lands on Earth The Register

PCI Express* Gen4 Retimer Supplemental Features and Standard

PCIe 4.0 will arrive in 2017 with double the bandwidth, but it will also boost the amount of power provided at the slot up to a minimum of 300W, which might eliminate the need for auxiliary power

Quickly test your Receiver Design to the PCIe 4.0 Base Specification Description. GRL’s PCI Express®4.0 Base Specification Receiver Calibration and Test Automation Software for the Anritsu MP1800A BERT (GRL-PCIE4-BASE-RXA) provides an automated, simple, and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

Software Version 4.0.0.1007 . Intel® Solid-State Drive PCIe* Driver July 2018 Release Notes 331995-006US 2 Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. Intel reserves these for future definition and shall have no

The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to be shared with device vendors.

Controller IP for PCIe 4

PCI Express 4.0 Technology Updates for Server and

SPECIFICATIONS PCIe-6738 PCI Express, 16-Bit, 32-Channel, 1 MS/s Analog Output Device Definitions Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty. Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty. • …

As of now, the PCI Express 4.0 standard has been finalized and officially released. The new protocol promises twice the per-lane bandwidth of PCI Express 3.0, allowing a GPU or other accelerator

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

High-Speed Serial Bus Interface Solution for PCI Express, Thunderbolt, USB Signal Quality Analyzer MP1800A Series . 2 • Traffic volumes at data centers are exploding due to the spread of cloud computing services. Consequently, faster interfaces such as 100 GbE, 400 GbE, InfiniBand EDR, etc., are being deployed for communications between the servers and network equipment, while on the …

The Cadence® SpeedBridge® Adapter for PCI Express® (PCIe®) 4.0 provides efficient driver and application-level testing for verifying emulated PCIe 4.0 designs with the actual ASIC/SoC software/ hardware, driver development, and application development.

2017 Microchip Technology Inc. DS00002484A-page 5 AN2484 Note 1: Jitter specification for PCIe 4.0 is <500 fsRMS. All values in the table are fsRMS.

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s.

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

PCIe 3.1 and 4.0 Specifications Revealed Ryan Martin / 6 years ago Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s Hardware .

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

The PCI Express® (PCIe®) standard has long been used in applications like personal computers, networking and workstations. Due to its many benefits such as reliability, low-power, latency and scalable bandwidth from 2.5 GT/s to 16 GT/s, the specification has evolved to also become prevalent in designs for storage, cloud computing, mobile and

PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 youtube.com

Intel® Solid State Drive Datacenter PCIe* Microsoft

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

Software Version 4.0.0.1007 . Intel® Solid-State Drive PCIe* Driver July 2018 Release Notes 331995-006US 2 Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. Intel reserves these for future definition and shall have no

PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s.

Description: Different Receiver Architectures: PCI Express 3.0 add-in Card RX CEM is only required to work at E-12 at one point of choosing with the reference spec channel (~ 20 dB).

You might already know that PCI Express 4.0 is on its way. Back at the PCI-SIG’s (Special Interest Group) DevCon event in June, it was announced that the standard was complete and undergoing review.

GRL-PCIE4-BASE-RXA is used for testing your PCIe® 4.0 Receiver to the Base (ASIC) Specification, while GRL-PCIE4-CEM-RXA is used for testing end products to the PCIe® 4.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE4-RXA provides a simple user interface to automate complex PCIe testing. The software runs on Windows 7 or higher oscilloscope or any PC OS, and significantly …

The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to be shared with device vendors.

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification. Download PDF for more information

The PCIe 4.0 specification was announced in June, and has now been published. PCIe 4.0’s major improvement over the previous specification is a maximum data rate of 16GT/s, as opposed to PCIe …

This specification describes the PCI Express archite… view more This specification describes the PCI Express architecture, interconnect attributes, fabric management, and the programming interface required to design and build systems and peripherals that are compliant with the PCI Express specification.

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

The Cadence® SpeedBridge® Adapter for PCI Express® (PCIe®) 4.0 provides efficient driver and application-level testing for verifying emulated PCIe 4.0 designs with the actual ASIC/SoC software/ hardware, driver development, and application development.

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification’s previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

PCI Express 4.0 Technology Updates for Server and

DesignWare PHY IP for PCI Express 4.0 Synopsys

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

The multi-channel DesignWare® PHY IP for PCI Express® 4.0 includes Synopsys’ high-speed, high-performance transceiver to meet today’s applications’ demands for higher bandwidth. The PHY provides a cost-effective solution that is designed to meet the needs of today’s high-speed chip-to-chip

The PCIe 4.0 specification is available free of charge to PCI-SIG member companies via the official website, though non-members wishing to dive down into the nitty-gritty will be disappointed to

Quickly test your Receiver Design to the PCIe 4.0 Base Specification Description. GRL’s PCI Express®4.0 Base Specification Receiver Calibration and Test Automation Software for the Anritsu MP1800A BERT (GRL-PCIE4-BASE-RXA) provides an automated, simple, and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

The PCIe 4.0 specification was announced in June, and has now been published. PCIe 4.0’s major improvement over the previous specification is a maximum data rate of 16GT/s, as opposed to PCIe …

The preceding PCIe 4.0 specification is designed with key functional enhancements that future-proof the PCIe architecture design, thereby accelerating speech and future design specifcations future

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

“The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations,

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

The Cadence® SpeedBridge® Adapter for PCI Express® (PCIe®) 4.0 provides efficient driver and application-level testing for verifying emulated PCIe 4.0 designs with the actual ASIC/SoC software/ hardware, driver development, and application development.

DesignWare IP for PCI Express 4.0 Draft 0.7 Synopsys

PCI Express* Gen4 Retimer Supplemental Features and Standard

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification’s previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

“The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations,

Software Version 4.0.0.1007 . Intel® Solid-State Drive PCIe* Driver July 2018 Release Notes 331995-006US 2 Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. Intel reserves these for future definition and shall have no

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

26/08/2016 · PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 / PCI Express GENERATION COMPARISON – Everything you need to know CHANNEL MAIN TEST RIG setup as following: Intel i9-9900K Processor purchase link

You might already know that PCI Express 4.0 is on its way. Back at the PCI-SIG’s (Special Interest Group) DevCon event in June, it was announced that the standard was complete and undergoing review.

Quickly test your Receiver Design to the PCIe 4.0 Base Specification Description. GRL’s PCI Express®4.0 Base Specification Receiver Calibration and Test Automation Software for the Anritsu MP1800A BERT (GRL-PCIE4-BASE-RXA) provides an automated, simple, and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

DesignWare IP for PCI Express 4.0 Draft 0.7 Synopsys

PCI-SIG finalises PCIe 4.0 specification teases early

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

The preceding PCIe 4.0 specification is designed with key functional enhancements that future-proof the PCIe architecture design, thereby accelerating speech and future design specifcations future

6 PCIe Express* (PCIe*) 4.0 Retimer Supplemental Features and Standard BGA Footprint June 2018 1 Introduction 1.1 Overview PCI Express* (PCIe*) 4.0 capable retimers extend the …

PCIe 4.0 will arrive in 2017 with double the bandwidth, but it will also boost the amount of power provided at the slot up to a minimum of 300W, which might eliminate the need for auxiliary power

The multi-channel DesignWare® PHY IP for PCI Express® 4.0 includes Synopsys’ high-speed, high-performance transceiver to meet today’s applications’ demands for higher bandwidth. The PHY provides a cost-effective solution that is designed to meet the needs of today’s high-speed chip-to-chip

PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s.

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

2017 Microchip Technology Inc. DS00002484A-page 5 AN2484 Note 1: Jitter specification for PCIe 4.0 is <500 fsRMS. All values in the table are fsRMS.

PCI-SIG members are welcome to access the PCIe 4.0 spec online at no cost through the PCI-SIG Specification Library. Non-members may purchase the specification here. PCIe 4.0 is a significant milestone, but we’re not resting.

You might already know that PCI Express 4.0 is on its way. Back at the PCI-SIG’s (Special Interest Group) DevCon event in June, it was announced that the standard was complete and undergoing review.

PCI-Express 4.0 has modified the filter scenarios for 2.5 G and 5 G, bringing them in alignment with the minimum 0.01 dB peaking seen in the 8 G and 16 G specifications. AN946: PCI-Express 4.0 …

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

SpeedBridge Adapter for PCIe 4 Cadence Design Systems

PCI SIG Releases PCI-Express Gen 4.0 Specifications

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

PCI Express® 4.0 and 3.0 Base Specification Receiver Test Tek.com Developed for Tektronix by Granite River Labs (GRL), PCI Express 4.0 and 3.0 Base Specification Receiver Calibration and Test software for the Tektronix BERTScope BSX (BSXPCI4BSE) provides an automated, simple and efficient way to test your PCIe Receiver to the Base (ASIC

6 PCIe Express* (PCIe*) 4.0 Retimer Supplemental Features and Standard BGA Footprint June 2018 1 Introduction 1.1 Overview PCI Express* (PCIe*) 4.0 capable retimers extend the …

The PCI Express® (PCIe®) standard has long been used in applications like personal computers, networking and workstations. Due to its many benefits such as reliability, low-power, latency and scalable bandwidth from 2.5 GT/s to 16 GT/s, the specification has evolved to also become prevalent in designs for storage, cloud computing, mobile and

PCI Express* Gen4 Retimer Supplemental Features intel.in

Microchip’s Clock Devices’ Compliance with PCIe 4

6 PCIe Express* (PCIe*) 4.0 Retimer Supplemental Features and Standard BGA Footprint June 2018 1 Introduction 1.1 Overview PCI Express* (PCIe*) 4.0 capable retimers extend the …

One is the official launch of the PCIe 4.0 specification that will take the baton from PCIe 3.0, and the other is early work on the standards eventual replacement, PCIe 5.0.

Software Version 4.0.0.1007 . Intel® Solid-State Drive PCIe* Driver July 2018 Release Notes 331995-006US 2 Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. Intel reserves these for future definition and shall have no

GRL-PCIE4-BASE-RXA is used for testing your PCIe® 4.0 Receiver to the Base (ASIC) Specification, while GRL-PCIE4-CEM-RXA is used for testing end products to the PCIe® 4.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE4-RXA provides a simple user interface to automate complex PCIe testing. The software runs on Windows 7 or higher oscilloscope or any PC OS, and significantly …

the specification was first released, largely due to its software compatibility with PCI, which had already permeated the embedded world. PCIe offers low cost, high performance and flexibility, and since embedded systems are largely built with the same components used in other, higher-volume markets, PCIe is an ideal way to con-nect together the components inside embedded systems. As with most

PCIe 4.0 will arrive in 2017 with double the bandwidth, but it will also boost the amount of power provided at the slot up to a minimum of 300W, which might eliminate the need for auxiliary power

Compliant with PCIe 4.0, 3.0, 2.1, and 1.1 specifications, the Controller IP has over 100 configuration features to customize the controller to the specific needs of any

Description: Different Receiver Architectures: PCI Express 3.0 add-in Card RX CEM is only required to work at E-12 at one point of choosing with the reference spec channel (~ 20 dB).

PCI-SIG Releases PCIe 4.0 Version 1.0 ServeTheHome

The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to be shared with device vendors.

PCI Express 4.0 Draft 0.7 & PIPE 4.4 Specifications What

Microchip’s Clock Devices’ Compliance with PCIe 4

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

Controller IP for PCIe 4

GRL’s PCI Express 4.0 Base Specification Receiver Calibration and Test Automation software for the Tektronix BERTScope BSA (GRL-PCIE4-BASE-RX) provides an automated, simple and efficient way to test your PCIe 4.0 Receiver to the Base (ASIC) Specification.

PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 youtube.com

SpeedBridge Adapter for PCIe 4 Cadence Design Systems

6 PCIe Express* (PCIe*) 4.0 Retimer Supplemental Features and Standard BGA Footprint June 2018 1 Introduction 1.1 Overview PCI Express* (PCIe*) 4.0 capable retimers extend the …

For the Tektronix BERTScope BSA and Real-Time Oscilloscope

PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 youtube.com

Fore! PCI Express 4.0 finally lands on Earth The Register

GRL-PCIE4-BASE-RXA is used for testing your PCIe® 4.0 Receiver to the Base (ASIC) Specification, while GRL-PCIE4-CEM-RXA is used for testing end products to the PCIe® 4.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE4-RXA provides a simple user interface to automate complex PCIe testing. The software runs on Windows 7 or higher oscilloscope or any PC OS, and significantly …

Controller IP for PCIe 4

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

PCIe 4 specifications arrive PC Perspective

High-Speed Serial Bus Interface Solution for PCI Express

The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to be shared with device vendors.

PCI Express* Gen4 Retimer Supplemental Features and Standard

PCI SIG Releases PCI-Express Gen 4.0 Specifications

One is the official launch of the PCIe 4.0 specification that will take the baton from PCIe 3.0, and the other is early work on the standards eventual replacement, PCIe 5.0.

Fore! PCI Express 4.0 finally lands on Earth The Register

PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 youtube.com

Controller IP for PCIe 4

To learn more about the PCIe 4.0, Rev. 0.9 specification, visit http://www.pcisig.com. About PCI-SIG PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards.

PCI Express 4.0 Draft 0.7 & PIPE 4.4 Specifications What

High-Speed Serial Bus Interface Solution for PCI Express

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

Microchip’s Clock Devices’ Compliance with PCIe 4

DesignWare IP for PCI Express 4.0 Draft 0.7 Synopsys

PCI-SIG finalises PCIe 4.0 specification teases early

“The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations,

For the Tektronix BERTScope BSA and Real-Time Oscilloscope

PCI Express* Gen4 Retimer Supplemental Features and Standard

Fore! PCI Express 4.0 finally lands on Earth The Register

The review draft PCI Express* Device Security Enhancements Specification Revision 0.71 defines PCIe* Device Firmware Measurement and PCIe* Device Authentication that enable a Host to query and verify the identity and capability of a PCIe* Device, to improve system security.

Fore! PCI Express 4.0 finally lands on Earth The Register

PCIe 5.0 Arriving in 2019 With 4x More ExtremeTech

PCI Express* Gen4 Retimer Supplemental Features intel.in

As of now, the PCI Express 4.0 standard has been finalized and officially released. The new protocol promises twice the per-lane bandwidth of PCI Express 3.0, allowing a GPU or other accelerator

High-Speed Serial Bus Interface Solution for PCI Express

SpeedBridge Adapter for PCIe 4 Cadence Design Systems

PCIe 5.0 Arriving in 2019 With 4x More ExtremeTech

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification’s previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

Controller IP for PCIe 4

SpeedBridge Adapter for PCIe 4 Cadence Design Systems

PCI-Express 4.0 has modified the filter scenarios for 2.5 G and 5 G, bringing them in alignment with the minimum 0.01 dB peaking seen in the 8 G and 16 G specifications. AN946: PCI-Express 4.0 …

Fore! PCI Express 4.0 finally lands on Earth The Register

PCIe 4 specifications arrive PC Perspective

Now the PCI-SIG has announced that PCIe 4.0 specification is finished, and it plans to have PCIe 5.0 ready to go by 2019, which is liable to cripple the 4.0 spec before it even gets out of the gate.

DesignWare PHY IP for PCI Express 4.0 Synopsys

PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 youtube.com

SPECIFICATIONS PCIe-6738 PCI Express, 16-Bit, 32-Channel, 1 MS/s Analog Output Device Definitions Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty. Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty. • …

PCI-SIG releases final specifications of PCIe 4.0 which

PCI Express 4.0 Technology Updates for Server and

PCIe 3.1 and 4.0 Specifications Revealed Ryan Martin / 6 years ago Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s Hardware .

PCIe 4.0 vs PCIe 3.0 vs PCIe 2.0 vs PCIe 1.0 youtube.com

Intel® Solid State Drive Datacenter PCIe* Microsoft

The preceding PCIe 4.0 specification is designed with key functional enhancements that future-proof the PCIe architecture design, thereby accelerating speech and future design specifcations future

PCI Express* Gen4 Retimer Supplemental Features and Standard

DesignWare IP for PCI Express 4.0 Draft 0.7 Synopsys

Intel® Solid State Drive Datacenter PCIe* Microsoft

Retimer is now part of PCI Express 4.0 base specification. PCI-SIG is expected to implement compliance program for testing retimers. PCI-SIG is expected to …

PCI-SIG finalises PCIe 4.0 specification teases early

PCIe 4.0 specification released MyBroadband

PCIe-6738 Specifications National Instruments

PCI-SIG have announced PCIe 4.0 is on the horizon, with up to 16GT/s or just a hair under 32GB/s transfer rate on a 16x slot. The new standard will also allow devices to use more power, the draw

High-Speed Serial Bus Interface Solution for PCI Express

PCIe 4 specifications arrive PC Perspective

PCI-SIG finalises PCIe 4.0 specification teases early

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

PCIe 4 specifications arrive PC Perspective

PCI Express® 4.0 Base Specification Receiver Test

Microchip’s Clock Devices’ Compliance with PCIe 4

The PCIe 4.0 specification does provide guidelines for the new challenge it presents. PCIe is far from being “just an interface,” however. Phenomenal throughputs have been achieved with every release by PCI-SIG, the PCIe standards body, and thanks to the efforts of the multitude of engineers working to turn the specification into products that work well together. Successfully implementing

Microchip’s Clock Devices’ Compliance with PCIe 4

PCI-SIG finalises PCIe 4.0 specification teases early

Controller IP for PCIe 4

6 PCIe Express* (PCIe*) 4.0 Retimer Supplemental Features and Standard BGA Footprint June 2018 1 Introduction 1.1 Overview PCI Express* (PCIe*) 4.0 capable retimers extend the …

Controller IP for PCIe 4

PCI Express 4.0 Technology Updates for Server and

PCI-Express 4.0 has modified the filter scenarios for 2.5 G and 5 G, bringing them in alignment with the minimum 0.01 dB peaking seen in the 8 G and 16 G specifications. AN946: PCI-Express 4.0 …

PCIe-6738 Specifications National Instruments

PCI Express* Gen4 Retimer Supplemental Features and Standard

PCI Express* Gen4 Retimer Supplemental Features intel.in

The PCIe 4.0 specification is available free of charge to PCI-SIG member companies via the official website, though non-members wishing to dive down into the nitty-gritty will be disappointed to

Intel® Solid State Drive Datacenter PCIe* Microsoft

Microchip’s Clock Devices’ Compliance with PCIe 4

As of now, the PCI Express 4.0 standard has been finalized and officially released. The new protocol promises twice the per-lane bandwidth of PCI Express 3.0, allowing a GPU or other accelerator

SpeedBridge Adapter for PCIe 4 Cadence Design Systems

PCI-SIG releases final specifications of PCIe 4.0 which

GRL-PCIE4-BASE-RXA is used for testing your PCIe® 4.0 Receiver to the Base (ASIC) Specification, while GRL-PCIE4-CEM-RXA is used for testing end products to the PCIe® 4.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE4-RXA provides a simple user interface to automate complex PCIe testing. The software runs on Windows 7 or higher oscilloscope or any PC OS, and significantly …

PCI-SIG finalises PCIe 4.0 specification teases early

PCI Express 4.0 Technology Updates for Server and

“The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations,

Controller IP for PCIe 4

PCI Express 4.0 Draft 0.7 Specification It is a Competitive Market – Finish First! The PCI-SIG specification development process freezes functionality at the Draft 0.7, which makes it the ideal time to start designing high-performance SoCs.

PCI Express* Gen4 Retimer Supplemental Features intel.in

High-Speed Serial Bus Interface Solution for PCI Express

The Peripheral Component Interconnect (PCI) special interest group (SIG) published the first official specification (version 1.0) of PCI-Express gen 4.0 bus. The specification’s previous draft 0.9 was under technical review by members of the SIG. The new generation PCIe …

PCI-SIG Releases PCIe 4.0 Version 1.0 ServeTheHome

PCI Express* Gen4 Retimer Supplemental Features intel.in

PCIe-6738 Specifications National Instruments

As of now, the PCI Express 4.0 standard has been finalized and officially released. The new protocol promises twice the per-lane bandwidth of PCI Express 3.0, allowing a GPU or other accelerator

PCI-SIG finalises PCIe 4.0 specification teases early

PCI Express 4.0 Technology Updates for Server and

Description: Different Receiver Architectures: PCI Express 3.0 add-in Card RX CEM is only required to work at E-12 at one point of choosing with the reference spec channel (~ 20 dB).

Controller IP for PCIe 4

PCI Express 4.0 Draft 0.7 & PIPE 4.4 Specifications What

PCIe 5.0 Arriving in 2019 With 4x More ExtremeTech

SPECIFICATIONS PCIe-6738 PCI Express, 16-Bit, 32-Channel, 1 MS/s Analog Output Device Definitions Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty. Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty. • …

PCIe 5.0 Arriving in 2019 With 4x More ExtremeTech

PCI-SIG Releases PCIe 4.0 Version 1.0 ServeTheHome

“The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations,

PCI Express 4.0 Draft 0.7 & PIPE 4.4 Specifications What

PCI-SIG Releases PCIe 4.0 Version 1.0 ServeTheHome

PCIe-6738 Specifications National Instruments

6 PCIe Express* (PCIe*) 4.0 Retimer Supplemental Features and Standard BGA Footprint June 2018 1 Introduction 1.1 Overview PCI Express* (PCIe*) 4.0 capable retimers extend the …

PCI-SIG Releases PCIe 4.0 Version 1.0 ServeTheHome