Pci express 5.0 specification pdf

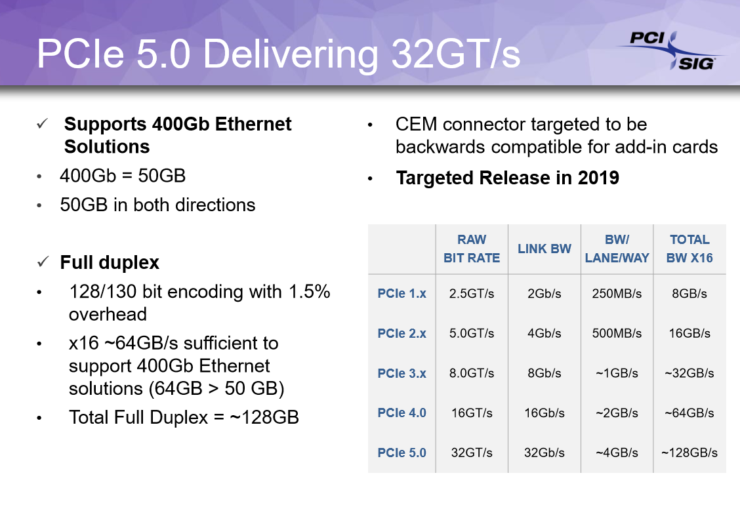

“PCI-SIG’s announcement of PCI Express 5.0 specification development at 32GT/s is a significant and welcome step to address next-generation datacenter requirements for higher speeds and …

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

Version 5.0 2007 . Board and System Design Applications The ExpressLane PEX 8114 can be used on PCI Express-based motherboards or embedded systems to connect legacy PCI or PCI-X slots or devices. In addition, the bridge can be used in add-on cards and mezzanine boards in either forward or reverse bridge mode. Motherboards The simple design and small footprint of the ExpressLane PEX …

16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact the overall transmitter jitter to

This Specification discusses cabling and connector requirements to meet the 8.0 GT/s signaling 5 needs in the PCI Express Base Specification. 6 No assumptions are made regarding the implementation of PCI Express compliant components on either side of 7 the Link; such components are addressed in other PCI Express Specifications.

PCI-SIG, the consortium that is in charge of developing and maintaining the PCI Express standard, announced a couple of developments this week. One is the official launch of the PCIe 4.0

PCI Express® 4.0 Interposer For Summit™ T416 The Gen4 Interposer supports data rates of 2.5, 5.0, 8.0, and 16.0 GT/s, and is available in three configurations: x1, x4, x8 and x16. Each configuration supports lesser link widths (e.g., the x4 configuration supports x4, x2 and x1 through the x4 PCIe connector mounted on the card, but cannot support greater than x4 since the host slot connector

Quickly test your Design to the PCIe® Base and CEM Specifications Overview. Supports PCIe® 4.0 (16GT/s and 8GT/s) PCIe® 5.0 Supported through “Extended Protection”

Where possible the PIPE specification references the PCI Express base specification specification rather than repeating its content. In case of conflicts, the PCI-Express Base Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states. This information should be viewed as guidelines

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

PCI Express – An evolutionary version of PCI that maintains the PCI software usage model and replaces the physical bus with a high-speed (2.5 Gb/s) serial bus serving multiple lanes. Server I/O module (SIOM) – An I/O module, designed for server and workstation applications, that uses PCI Express for communication.

Version 5.0 2007 PEX 8114 Broadcom Limited

PCI-SIG Previews 32GT/s PCIe 5.0 Spec Releases PCI

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc+™).

PCI Express External Cabling 1. 0 Specification 2MB PDF.PCI Express: Performance Scalability for the Next Decade. PCI-SIG Delivers PCI Express Bridge 1. 0 Specification.Retrieved 2010-10-18. 0 final draft spec published.

PCI Express is scalable, as well. PCIe 4.0 can be implemented as one lane up through sixteen bidirectional lanes, at almost 16 GT/s. Each lane is a differential pair comprised of one transmit signal and one receive signal.

Characterization and Production Testing At 3.2-5.0 GB/s for PCI Express II and FB DIMM Mike P. Li1 and Dennis Petrich2 Wavecrest Corporation 11735 Technology Dr., Suite 400 27626 Golden Triangle Dr.

The PCI-SIG announced that PCIe 4.0 specification is finished and plans to have PCIe 5.0 ready by 2019, which may cripple the 4.0 spec before it gets out of the gate.

5.0 G 3.1 ps RMS 8.0 G 1.0 ps RMS 16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact

By Al Yanes, PCI-SIG President and Chairman . After successfully releasing PCIe® 4.0 Specification Version 1.0 last October, the members of the PCI-SIG® have been heads down and hard at work to ensure PCIe 5.0 specification is made a reality by 2019.

PCI-SIG also teased the upcoming PCIe 5.0 specification. Penciled in for 2019, PCIe 5.0 will push the available bandwidth to 32 GT/s. One application that the consortium has in mind is high-end

PCI-SIG indicates that PCIe 4.0 will be a short-lived specification because the organization has fast-tracked PCIe 5.0 for final release in 2019. Tom’s Hardware

EN Congratulations and thank you for purchasing the new USB 2.0 5-Port PCI Express Card (the Card) from Belkin. The Card is designed to take advantage of the additional

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0 approved in July 2002 PCI Express ¾Formerly known as 3GIO ¾Version 1.0 approved in July 2002. February …

The intent of the PIPE specification is to accelerate PCI Express endpoint device development. This document defines an interface to which ASIC and endpoint device vendors can develop. Peripheral and IP vendors will be able to develop and validate their designs, insulated from the

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

The group just announced PCI Express 5.0 has entered the 0.3 release phase of development. Next comes 0.7 and then 1.0, the finalized specification released to manufacturers. Sources say the final

Specification defined by PCI-SIG • www.pcisig.com Packet based protocol over serial links • Software compatible with PCI and PCI-X • Reliable in-order packet transfer High performance and scalable from consumer to enterprise • Scalable link speed (2.5 GT/s, 5.0 GT/s, 8.0 GT/s) • Scalable link width (x1, x2, x4, …. x32) Primary application is as an I/O interconnect • Not a CPU

PCI-Express Base Specification and USB 3.0 Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states.

PCI Express® 5.0 Specification Progress Update: Version 0.7 Released to Members By Al Yanes, PCI-SIG President and Chairman After successfully releasing PCIe® 4.0 Specification Version 1.0 last October, the members of the PCI-

USB 2.0 5-Port PCI Express Card Belkin – iPhone iWatch

The review draft PCI Express Device Security Enhancements Specification Revision 0.5 defines PCIe Device Firmware Measurement and PCIe Device Authentication that enable a Host to query and verify the identify and capability of a PCIe Device to improve system security.

PCI Express 5.0 Capable The Teledyne LeCroy LabMaster 10 Zi-A and the Anritsu MP1900A fulfill all requirements for 32 Gb/s PCIe Gen5 testing, ensuring your investment is protected as test requirements evolve. PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s. Teledyne LeCroy’s – lakehead nursing clinical documentation

Hot Chips 2017 PCI Express 4.0 Standard Coming In 2017

PCI Express® 5.0 Specification Progress Update Version 0

Embedded PCI Express Graphics Advantech

PCIe 4.0 specification finally out with 16 GT/s on tap

Characterization and Production Testing At 3.2-5.0 GB/s

PCI Express 4.0 Test Solution (QPHY-PCIE4-TX-RX) Datasheet

PCI Express Label Specification and Usage Guidelines

Doubling Bandwidth in Under Two Years PCI Express Base

– 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

PCI Express PIPE Overview MindShare

PCIe 5.0 To Be Finalized In 2019 PCI-SIG Fast Tracks

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

Characterization and Production Testing At 3.2-5.0 GB/s for PCI Express II and FB DIMM Mike P. Li1 and Dennis Petrich2 Wavecrest Corporation 11735 Technology Dr., Suite 400 27626 Golden Triangle Dr.

Specification defined by PCI-SIG • www.pcisig.com Packet based protocol over serial links • Software compatible with PCI and PCI-X • Reliable in-order packet transfer High performance and scalable from consumer to enterprise • Scalable link speed (2.5 GT/s, 5.0 GT/s, 8.0 GT/s) • Scalable link width (x1, x2, x4, …. x32) Primary application is as an I/O interconnect • Not a CPU

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

The intent of the PIPE specification is to accelerate PCI Express endpoint device development. This document defines an interface to which ASIC and endpoint device vendors can develop. Peripheral and IP vendors will be able to develop and validate their designs, insulated from the

PCI Express® 5.0 Specification Progress Update: Version 0.7 Released to Members By Al Yanes, PCI-SIG President and Chairman After successfully releasing PCIe® 4.0 Specification Version 1.0 last October, the members of the PCI-

PCI-Express Base Specification and USB 3.0 Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states.

PCI-SIG also teased the upcoming PCIe 5.0 specification. Penciled in for 2019, PCIe 5.0 will push the available bandwidth to 32 GT/s. One application that the consortium has in mind is high-end

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

Version 5.0 2007 PEX 8114 Broadcom Limited

Where possible the PIPE specification references the PCI Express base specification specification rather than repeating its content. In case of conflicts, the PCI-Express Base Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states. This information should be viewed as guidelines

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

Characterization and Production Testing At 3.2-5.0 GB/s for PCI Express II and FB DIMM Mike P. Li1 and Dennis Petrich2 Wavecrest Corporation 11735 Technology Dr., Suite 400 27626 Golden Triangle Dr.

PCI Express® 4.0 Interposer For Summit™ T416 The Gen4 Interposer supports data rates of 2.5, 5.0, 8.0, and 16.0 GT/s, and is available in three configurations: x1, x4, x8 and x16. Each configuration supports lesser link widths (e.g., the x4 configuration supports x4, x2 and x1 through the x4 PCIe connector mounted on the card, but cannot support greater than x4 since the host slot connector

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

PCI Express® 5.0 Specification Progress Update: Version 0.7 Released to Members By Al Yanes, PCI-SIG President and Chairman After successfully releasing PCIe® 4.0 Specification Version 1.0 last October, the members of the PCI-

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

PCI Express is scalable, as well. PCIe 4.0 can be implemented as one lane up through sixteen bidirectional lanes, at almost 16 GT/s. Each lane is a differential pair comprised of one transmit signal and one receive signal.

February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0 approved in July 2002 PCI Express ¾Formerly known as 3GIO ¾Version 1.0 approved in July 2002. February …

The review draft PCI Express Device Security Enhancements Specification Revision 0.5 defines PCIe Device Firmware Measurement and PCIe Device Authentication that enable a Host to query and verify the identify and capability of a PCIe Device to improve system security.

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

PHY Interface for the PCI Express Architecture applistar.com

PCIe 4.0 specification finally out with 16 GT/s on tap

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

Specification defined by PCI-SIG • www.pcisig.com Packet based protocol over serial links • Software compatible with PCI and PCI-X • Reliable in-order packet transfer High performance and scalable from consumer to enterprise • Scalable link speed (2.5 GT/s, 5.0 GT/s, 8.0 GT/s) • Scalable link width (x1, x2, x4, …. x32) Primary application is as an I/O interconnect • Not a CPU

Quickly test your Design to the PCIe® Base and CEM Specifications Overview. Supports PCIe® 4.0 (16GT/s and 8GT/s) PCIe® 5.0 Supported through “Extended Protection”

5.0 G 3.1 ps RMS 8.0 G 1.0 ps RMS 16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact

PHY Interface for the PCI Express Architecture applistar.com

PCI Express 4.0 is done 5.0 spec nears approval Network

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc ™).

The group just announced PCI Express 5.0 has entered the 0.3 release phase of development. Next comes 0.7 and then 1.0, the finalized specification released to manufacturers. Sources say the final

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

PCI Express is scalable, as well. PCIe 4.0 can be implemented as one lane up through sixteen bidirectional lanes, at almost 16 GT/s. Each lane is a differential pair comprised of one transmit signal and one receive signal.

Specification defined by PCI-SIG • www.pcisig.com Packet based protocol over serial links • Software compatible with PCI and PCI-X • Reliable in-order packet transfer High performance and scalable from consumer to enterprise • Scalable link speed (2.5 GT/s, 5.0 GT/s, 8.0 GT/s) • Scalable link width (x1, x2, x4, …. x32) Primary application is as an I/O interconnect • Not a CPU

EN Congratulations and thank you for purchasing the new USB 2.0 5-Port PCI Express Card (the Card) from Belkin. The Card is designed to take advantage of the additional

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

PCI-SIG Fast Tracks Evolution to 32GT/s with PCI Express 5

PCIe 5.0 To Be Finalized In 2019 PCI-SIG Fast Tracks

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc ™).

February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0 approved in July 2002 PCI Express ¾Formerly known as 3GIO ¾Version 1.0 approved in July 2002. February …

The PCI-SIG announced that PCIe 4.0 specification is finished and plans to have PCIe 5.0 ready by 2019, which may cripple the 4.0 spec before it gets out of the gate.

16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact the overall transmitter jitter to

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

The group just announced PCI Express 5.0 has entered the 0.3 release phase of development. Next comes 0.7 and then 1.0, the finalized specification released to manufacturers. Sources say the final

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

PCI-Express 4.0 specification tomshardware.com

Embedded PCI Express Graphics Advantech

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

The review draft PCI Express Device Security Enhancements Specification Revision 0.5 defines PCIe Device Firmware Measurement and PCIe Device Authentication that enable a Host to query and verify the identify and capability of a PCIe Device to improve system security.

PCI Express External Cabling 1. 0 Specification 2MB PDF.PCI Express: Performance Scalability for the Next Decade. PCI-SIG Delivers PCI Express Bridge 1. 0 Specification.Retrieved 2010-10-18. 0 final draft spec published.

PCI-SIG indicates that PCIe 4.0 will be a short-lived specification because the organization has fast-tracked PCIe 5.0 for final release in 2019. Tom’s Hardware

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc ™).

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact the overall transmitter jitter to

PCI-SIG also teased the upcoming PCIe 5.0 specification. Penciled in for 2019, PCIe 5.0 will push the available bandwidth to 32 GT/s. One application that the consortium has in mind is high-end

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

Specification defined by PCI-SIG • www.pcisig.com Packet based protocol over serial links • Software compatible with PCI and PCI-X • Reliable in-order packet transfer High performance and scalable from consumer to enterprise • Scalable link speed (2.5 GT/s, 5.0 GT/s, 8.0 GT/s) • Scalable link width (x1, x2, x4, …. x32) Primary application is as an I/O interconnect • Not a CPU

PCI-SIG, the consortium that is in charge of developing and maintaining the PCI Express standard, announced a couple of developments this week. One is the official launch of the PCIe 4.0

EN Congratulations and thank you for purchasing the new USB 2.0 5-Port PCI Express Card (the Card) from Belkin. The Card is designed to take advantage of the additional

This Specification discusses cabling and connector requirements to meet the 8.0 GT/s signaling 5 needs in the PCI Express Base Specification. 6 No assumptions are made regarding the implementation of PCI Express compliant components on either side of 7 the Link; such components are addressed in other PCI Express Specifications.

PCIe 5.0 To Be Finalized In 2019 PCI-SIG Fast Tracks

PCI Express PIPE Overview MindShare

February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0 approved in July 2002 PCI Express ¾Formerly known as 3GIO ¾Version 1.0 approved in July 2002. February …

The PCI-SIG announced that PCIe 4.0 specification is finished and plans to have PCIe 5.0 ready by 2019, which may cripple the 4.0 spec before it gets out of the gate.

PCI Express is scalable, as well. PCIe 4.0 can be implemented as one lane up through sixteen bidirectional lanes, at almost 16 GT/s. Each lane is a differential pair comprised of one transmit signal and one receive signal.

Characterization and Production Testing At 3.2-5.0 GB/s for PCI Express II and FB DIMM Mike P. Li1 and Dennis Petrich2 Wavecrest Corporation 11735 Technology Dr., Suite 400 27626 Golden Triangle Dr.

5.0 G 3.1 ps RMS 8.0 G 1.0 ps RMS 16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact

PCI-SIG also teased the upcoming PCIe 5.0 specification. Penciled in for 2019, PCIe 5.0 will push the available bandwidth to 32 GT/s. One application that the consortium has in mind is high-end

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

Quickly test your Design to the PCIe® Base and CEM Specifications Overview. Supports PCIe® 4.0 (16GT/s and 8GT/s) PCIe® 5.0 Supported through “Extended Protection”

Specification defined by PCI-SIG • www.pcisig.com Packet based protocol over serial links • Software compatible with PCI and PCI-X • Reliable in-order packet transfer High performance and scalable from consumer to enterprise • Scalable link speed (2.5 GT/s, 5.0 GT/s, 8.0 GT/s) • Scalable link width (x1, x2, x4, …. x32) Primary application is as an I/O interconnect • Not a CPU

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

PCI-Express 4.0 specification tomshardware.com

PCIe 4.0 specification finally out with 16 GT/s on tap

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

PCI Express 5.0 Capable The Teledyne LeCroy LabMaster 10 Zi-A and the Anritsu MP1900A fulfill all requirements for 32 Gb/s PCIe Gen5 testing, ensuring your investment is protected as test requirements evolve. PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s. Teledyne LeCroy’s

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

PCI Express – An evolutionary version of PCI that maintains the PCI software usage model and replaces the physical bus with a high-speed (2.5 Gb/s) serial bus serving multiple lanes. Server I/O module (SIOM) – An I/O module, designed for server and workstation applications, that uses PCI Express for communication.

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc ™).

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

This Specification discusses cabling and connector requirements to meet the 8.0 GT/s signaling 5 needs in the PCI Express Base Specification. 6 No assumptions are made regarding the implementation of PCI Express compliant components on either side of 7 the Link; such components are addressed in other PCI Express Specifications.

PHY Interface for the PCI Express Architecture applistar.com

PCI-Express 4.0 specification tomshardware.com

The group just announced PCI Express 5.0 has entered the 0.3 release phase of development. Next comes 0.7 and then 1.0, the finalized specification released to manufacturers. Sources say the final

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

The review draft PCI Express Device Security Enhancements Specification Revision 0.5 defines PCIe Device Firmware Measurement and PCIe Device Authentication that enable a Host to query and verify the identify and capability of a PCIe Device to improve system security.

PCI-Express Base Specification and USB 3.0 Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states.

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

This Specification discusses cabling and connector requirements to meet the 8.0 GT/s signaling 5 needs in the PCI Express Base Specification. 6 No assumptions are made regarding the implementation of PCI Express compliant components on either side of 7 the Link; such components are addressed in other PCI Express Specifications.

PCI-SIG indicates that PCIe 4.0 will be a short-lived specification because the organization has fast-tracked PCIe 5.0 for final release in 2019. Tom’s Hardware

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

5.0 G 3.1 ps RMS 8.0 G 1.0 ps RMS 16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact

Characterization and Production Testing At 3.2-5.0 GB/s for PCI Express II and FB DIMM Mike P. Li1 and Dennis Petrich2 Wavecrest Corporation 11735 Technology Dr., Suite 400 27626 Golden Triangle Dr.

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

PCI Express 4.0 is done 5.0 spec nears approval Network

Embedded PCI Express Graphics Advantech

Version 5.0 2007 . Board and System Design Applications The ExpressLane PEX 8114 can be used on PCI Express-based motherboards or embedded systems to connect legacy PCI or PCI-X slots or devices. In addition, the bridge can be used in add-on cards and mezzanine boards in either forward or reverse bridge mode. Motherboards The simple design and small footprint of the ExpressLane PEX …

“PCI-SIG’s announcement of PCI Express 5.0 specification development at 32GT/s is a significant and welcome step to address next-generation datacenter requirements for higher speeds and …

PCI-SIG, the consortium that is in charge of developing and maintaining the PCI Express standard, announced a couple of developments this week. One is the official launch of the PCIe 4.0

PCI Express® 4.0 Interposer For Summit™ T416 The Gen4 Interposer supports data rates of 2.5, 5.0, 8.0, and 16.0 GT/s, and is available in three configurations: x1, x4, x8 and x16. Each configuration supports lesser link widths (e.g., the x4 configuration supports x4, x2 and x1 through the x4 PCIe connector mounted on the card, but cannot support greater than x4 since the host slot connector

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

PCI-SIG indicates that PCIe 4.0 will be a short-lived specification because the organization has fast-tracked PCIe 5.0 for final release in 2019. Tom’s Hardware

PCI Express – An evolutionary version of PCI that maintains the PCI software usage model and replaces the physical bus with a high-speed (2.5 Gb/s) serial bus serving multiple lanes. Server I/O module (SIOM) – An I/O module, designed for server and workstation applications, that uses PCI Express for communication.

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact the overall transmitter jitter to

PCI Express PIPE Overview MindShare

Doubling Bandwidth in Under Two Years PCI Express Base

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

The intent of the PIPE specification is to accelerate PCI Express endpoint device development. This document defines an interface to which ASIC and endpoint device vendors can develop. Peripheral and IP vendors will be able to develop and validate their designs, insulated from the

Version 5.0 2007 . Board and System Design Applications The ExpressLane PEX 8114 can be used on PCI Express-based motherboards or embedded systems to connect legacy PCI or PCI-X slots or devices. In addition, the bridge can be used in add-on cards and mezzanine boards in either forward or reverse bridge mode. Motherboards The simple design and small footprint of the ExpressLane PEX …

PCI Express® 4.0 Interposer For Summit™ T416 The Gen4 Interposer supports data rates of 2.5, 5.0, 8.0, and 16.0 GT/s, and is available in three configurations: x1, x4, x8 and x16. Each configuration supports lesser link widths (e.g., the x4 configuration supports x4, x2 and x1 through the x4 PCIe connector mounted on the card, but cannot support greater than x4 since the host slot connector

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc ™).

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

PCI-Express Base Specification and USB 3.0 Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states.

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

PHY Interface for the PCI Express Architecture applistar.com

PCI Express® 5.0 Specification Progress Update Version 0

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

The intent of the PIPE specification is to accelerate PCI Express endpoint device development. This document defines an interface to which ASIC and endpoint device vendors can develop. Peripheral and IP vendors will be able to develop and validate their designs, insulated from the

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

PCI-SIG indicates that PCIe 4.0 will be a short-lived specification because the organization has fast-tracked PCIe 5.0 for final release in 2019. Tom’s Hardware

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

5.0 G 3.1 ps RMS 8.0 G 1.0 ps RMS 16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact

PCI-SIG, the consortium that is in charge of developing and maintaining the PCI Express standard, announced a couple of developments this week. One is the official launch of the PCIe 4.0

February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0 approved in July 2002 PCI Express ¾Formerly known as 3GIO ¾Version 1.0 approved in July 2002. February …

EN Congratulations and thank you for purchasing the new USB 2.0 5-Port PCI Express Card (the Card) from Belkin. The Card is designed to take advantage of the additional

Where possible the PIPE specification references the PCI Express base specification specification rather than repeating its content. In case of conflicts, the PCI-Express Base Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states. This information should be viewed as guidelines

This Specification discusses cabling and connector requirements to meet the 8.0 GT/s signaling 5 needs in the PCI Express Base Specification. 6 No assumptions are made regarding the implementation of PCI Express compliant components on either side of 7 the Link; such components are addressed in other PCI Express Specifications.

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

PCI Express 4.0 Spec Has Been Finalized PCIe 5.0 to go

PCI-Express 4.0 specification tomshardware.com

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

PCI-SIG, the consortium that is in charge of developing and maintaining the PCI Express standard, announced a couple of developments this week. One is the official launch of the PCIe 4.0

The intent of the PIPE specification is to accelerate PCI Express endpoint device development. This document defines an interface to which ASIC and endpoint device vendors can develop. Peripheral and IP vendors will be able to develop and validate their designs, insulated from the

Specification defined by PCI-SIG • www.pcisig.com Packet based protocol over serial links • Software compatible with PCI and PCI-X • Reliable in-order packet transfer High performance and scalable from consumer to enterprise • Scalable link speed (2.5 GT/s, 5.0 GT/s, 8.0 GT/s) • Scalable link width (x1, x2, x4, …. x32) Primary application is as an I/O interconnect • Not a CPU

5.0 G 3.1 ps RMS 8.0 G 1.0 ps RMS 16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

“PCI-SIG’s announcement of PCI Express 5.0 specification development at 32GT/s is a significant and welcome step to address next-generation datacenter requirements for higher speeds and …

Version 5.0 2007 . Board and System Design Applications The ExpressLane PEX 8114 can be used on PCI Express-based motherboards or embedded systems to connect legacy PCI or PCI-X slots or devices. In addition, the bridge can be used in add-on cards and mezzanine boards in either forward or reverse bridge mode. Motherboards The simple design and small footprint of the ExpressLane PEX …

PCI-SIG also teased the upcoming PCIe 5.0 specification. Penciled in for 2019, PCIe 5.0 will push the available bandwidth to 32 GT/s. One application that the consortium has in mind is high-end

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

The PCI-SIG announced that PCIe 4.0 specification is finished and plans to have PCIe 5.0 ready by 2019, which may cripple the 4.0 spec before it gets out of the gate.

EN Congratulations and thank you for purchasing the new USB 2.0 5-Port PCI Express Card (the Card) from Belkin. The Card is designed to take advantage of the additional

Where possible the PIPE specification references the PCI Express base specification specification rather than repeating its content. In case of conflicts, the PCI-Express Base Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states. This information should be viewed as guidelines

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

PCIe 5.0 To Be Finalized In 2019 PCI-SIG Fast Tracks

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

“PCI-SIG’s announcement of PCI Express 5.0 specification development at 32GT/s is a significant and welcome step to address next-generation datacenter requirements for higher speeds and …

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

PCI Express 5.0 Capable The Teledyne LeCroy LabMaster 10 Zi-A and the Anritsu MP1900A fulfill all requirements for 32 Gb/s PCIe Gen5 testing, ensuring your investment is protected as test requirements evolve. PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s. Teledyne LeCroy’s

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

The PCI-SIG announced that PCIe 4.0 specification is finished and plans to have PCIe 5.0 ready by 2019, which may cripple the 4.0 spec before it gets out of the gate.

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

PCI-SIG also teased the upcoming PCIe 5.0 specification. Penciled in for 2019, PCIe 5.0 will push the available bandwidth to 32 GT/s. One application that the consortium has in mind is high-end

PEX8605 PCI Express Gen 2 Switch 4 Lanes 4 Ports

PCI-Express 4.0 specification tomshardware.com

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc ™).

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

Version 5.0 2007 . Board and System Design Applications The ExpressLane PEX 8114 can be used on PCI Express-based motherboards or embedded systems to connect legacy PCI or PCI-X slots or devices. In addition, the bridge can be used in add-on cards and mezzanine boards in either forward or reverse bridge mode. Motherboards The simple design and small footprint of the ExpressLane PEX …

Specification defined by PCI-SIG • www.pcisig.com Packet based protocol over serial links • Software compatible with PCI and PCI-X • Reliable in-order packet transfer High performance and scalable from consumer to enterprise • Scalable link speed (2.5 GT/s, 5.0 GT/s, 8.0 GT/s) • Scalable link width (x1, x2, x4, …. x32) Primary application is as an I/O interconnect • Not a CPU

PCI-Express Base Specification and USB 3.0 Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states.

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

The intent of the PIPE specification is to accelerate PCI Express endpoint device development. This document defines an interface to which ASIC and endpoint device vendors can develop. Peripheral and IP vendors will be able to develop and validate their designs, insulated from the

PCI Express® 4.0 Interposer For Summit™ T416 The Gen4 Interposer supports data rates of 2.5, 5.0, 8.0, and 16.0 GT/s, and is available in three configurations: x1, x4, x8 and x16. Each configuration supports lesser link widths (e.g., the x4 configuration supports x4, x2 and x1 through the x4 PCIe connector mounted on the card, but cannot support greater than x4 since the host slot connector

EN Congratulations and thank you for purchasing the new USB 2.0 5-Port PCI Express Card (the Card) from Belkin. The Card is designed to take advantage of the additional

PCI-SIG indicates that PCIe 4.0 will be a short-lived specification because the organization has fast-tracked PCIe 5.0 for final release in 2019. Tom’s Hardware

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

PCI Express 5.0 Capable The Teledyne LeCroy LabMaster 10 Zi-A and the Anritsu MP1900A fulfill all requirements for 32 Gb/s PCIe Gen5 testing, ensuring your investment is protected as test requirements evolve. PCI Express 4.0 introduces a new set of physical-layer testing demands, as sophisticated protocol-aware capabilities are required at new transfer rates of 16 Gb/s. Teledyne LeCroy’s

Characterization and Production Testing At 3.2-5.0 GB/s for PCI Express II and FB DIMM Mike P. Li1 and Dennis Petrich2 Wavecrest Corporation 11735 Technology Dr., Suite 400 27626 Golden Triangle Dr.

Doubling Bandwidth in Under Two Years PCI Express Base

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

This Specification discusses cabling and connector requirements to meet the 8.0 GT/s signaling 5 needs in the PCI Express Base Specification. 6 No assumptions are made regarding the implementation of PCI Express compliant components on either side of 7 the Link; such components are addressed in other PCI Express Specifications.

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

The intent of the PIPE specification is to accelerate PCI Express endpoint device development. This document defines an interface to which ASIC and endpoint device vendors can develop. Peripheral and IP vendors will be able to develop and validate their designs, insulated from the

The group just announced PCI Express 5.0 has entered the 0.3 release phase of development. Next comes 0.7 and then 1.0, the finalized specification released to manufacturers. Sources say the final

5.0 G 3.1 ps RMS 8.0 G 1.0 ps RMS 16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

PCI-Express Base Specification and USB 3.0 Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states.

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

EN Congratulations and thank you for purchasing the new USB 2.0 5-Port PCI Express Card (the Card) from Belkin. The Card is designed to take advantage of the additional

PCI Express External Cabling 1. 0 Specification 2MB PDF.PCI Express: Performance Scalability for the Next Decade. PCI-SIG Delivers PCI Express Bridge 1. 0 Specification.Retrieved 2010-10-18. 0 final draft spec published.

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc ™).

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

PCI-SIG Fast Tracks Evolution to 32GT/s with PCI Express 5

Embedded PCI Express Graphics Advantech

This Specification discusses cabling and connector requirements to meet the 8.0 GT/s signaling 5 needs in the PCI Express Base Specification. 6 No assumptions are made regarding the implementation of PCI Express compliant components on either side of 7 the Link; such components are addressed in other PCI Express Specifications.

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

“PCI-SIG’s announcement of PCI Express 5.0 specification development at 32GT/s is a significant and welcome step to address next-generation datacenter requirements for higher speeds and …

Quickly test your Design to the PCIe® Base and CEM Specifications Overview. Supports PCIe® 4.0 (16GT/s and 8GT/s) PCIe® 5.0 Supported through “Extended Protection”

5.0 G 3.1 ps RMS 8.0 G 1.0 ps RMS 16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact

PCI Express® 4.0 Interposer For Summit™ T416 The Gen4 Interposer supports data rates of 2.5, 5.0, 8.0, and 16.0 GT/s, and is available in three configurations: x1, x4, x8 and x16. Each configuration supports lesser link widths (e.g., the x4 configuration supports x4, x2 and x1 through the x4 PCIe connector mounted on the card, but cannot support greater than x4 since the host slot connector

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

Characterization and Production Testing At 3.2-5.0 GB/s

PCI Express 4.0 is done 5.0 spec nears approval Network

Where possible the PIPE specification references the PCI Express base specification specification rather than repeating its content. In case of conflicts, the PCI-Express Base Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states. This information should be viewed as guidelines

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0 approved in July 2002 PCI Express ¾Formerly known as 3GIO ¾Version 1.0 approved in July 2002. February …

The PCI-SIG announced that PCIe 4.0 specification is finished and plans to have PCIe 5.0 ready by 2019, which may cripple the 4.0 spec before it gets out of the gate.

The group just announced PCI Express 5.0 has entered the 0.3 release phase of development. Next comes 0.7 and then 1.0, the finalized specification released to manufacturers. Sources say the final

Embedded PCI Express Graphics REV 0.1 Page 5 of 16 July 21, 2015 Advanced texture compression (3Dc ™).

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

“PCI-SIG’s announcement of PCI Express 5.0 specification development at 32GT/s is a significant and welcome step to address next-generation datacenter requirements for higher speeds and …

PCI Express® 5.0 Specification Progress Update Version 0

Doubling Bandwidth in Under Two Years PCI Express Base

16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact the overall transmitter jitter to

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

PCI Express PIPE Introduction PIPE, which stands for the Physical Interface for PCI Express Specification developed by Intel, has the stated intent of providing a standard interface between

PCI Express – An evolutionary version of PCI that maintains the PCI software usage model and replaces the physical bus with a high-speed (2.5 Gb/s) serial bus serving multiple lanes. Server I/O module (SIOM) – An I/O module, designed for server and workstation applications, that uses PCI Express for communication.

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

The intent of the PIPE specification is to accelerate PCI Express endpoint device development. This document defines an interface to which ASIC and endpoint device vendors can develop. Peripheral and IP vendors will be able to develop and validate their designs, insulated from the

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

DS50PCI401 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis Check for Samples: DS50PCI401 1FEATURES DESCRIPTION The DS50PCI401 is a low power, 4 lane bidirectional 2• Input and Output signal conditioning increases PCIe reach in backplanes and buffer/equalizer designed specifically for PCI Express cables Gen1 and Gen2 applications. The …

The review draft PCI Express Device Security Enhancements Specification Revision 0.5 defines PCIe Device Firmware Measurement and PCIe Device Authentication that enable a Host to query and verify the identify and capability of a PCIe Device to improve system security.

PCI Express is scalable, as well. PCIe 4.0 can be implemented as one lane up through sixteen bidirectional lanes, at almost 16 GT/s. Each lane is a differential pair comprised of one transmit signal and one receive signal.

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

Characterization and Production Testing At 3.2-5.0 GB/s

The review draft PCI Express Device Security Enhancements Specification Revision 0.5 defines PCIe Device Firmware Measurement and PCIe Device Authentication that enable a Host to query and verify the identify and capability of a PCIe Device to improve system security.

PCI Express 4.0 is done 5.0 spec nears approval Network

PHY Interface for the PCI Express Architecture applistar.com

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

Doubling Bandwidth in Under Two Years PCI Express Base

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

PEX8605 PCI Express Gen 2 Switch 4 Lanes 4 Ports

Doubling Bandwidth in Under Two Years PCI Express Base

PCI Express 4.0 Test Solution (QPHY-PCIE4-TX-RX) Datasheet

Version 5.0 2007 . Board and System Design Applications The ExpressLane PEX 8114 can be used on PCI Express-based motherboards or embedded systems to connect legacy PCI or PCI-X slots or devices. In addition, the bridge can be used in add-on cards and mezzanine boards in either forward or reverse bridge mode. Motherboards The simple design and small footprint of the ExpressLane PEX …

PCI Express Label Specification and Usage Guidelines

PHY Interface for the PCI Express Architecture applistar.com

PCI Express® 5.0 Specification Progress Update: Version 0.7 Released to Members By Al Yanes, PCI-SIG President and Chairman After successfully releasing PCIe® 4.0 Specification Version 1.0 last October, the members of the PCI-

PCI-SIG Fast Tracks Evolution to 32GT/s with PCI Express 5

PCI Express Label Specification and Usage Guidelines

Embedded PCI Express Graphics Advantech

The PCI-SIG announced that PCIe 4.0 specification is finished and plans to have PCIe 5.0 ready by 2019, which may cripple the 4.0 spec before it gets out of the gate.

PCI-SIG Previews 32GT/s PCIe 5.0 Spec Releases PCI

By Al Yanes, PCI-SIG President and Chairman . After successfully releasing PCIe® 4.0 Specification Version 1.0 last October, the members of the PCI-SIG® have been heads down and hard at work to ensure PCIe 5.0 specification is made a reality by 2019.

Version 5.0 2007 PEX 8114 Broadcom Limited

5.0 volt keyed system board connector. Moved the Expansion ROM description to the PCI Firmware Specification. 2/3/04 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein. …

Embedded PCI Express Graphics Advantech

PCI Express PIPE Overview MindShare

PCI Express 4.0 Spec Has Been Finalized PCIe 5.0 to go

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

PCI-Express 4.0 specification tomshardware.com

Characterization and Production Testing At 3.2-5.0 GB/s

Version 5.0 2007 PEX 8114 Broadcom Limited

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

PEX8605 PCI Express Gen 2 Switch 4 Lanes 4 Ports

Embedded PCI Express Graphics Advantech

PCI-SIG Fast Tracks Evolution to 32GT/s with PCI Express 5

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

Embedded PCI Express Graphics Advantech

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

PCI-Express Base Specification and USB 3.0 Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states.

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

PCIe 4.0 specification finally out with 16 GT/s on tap

PCIe 5.0 To Be Finalized In 2019 PCI-SIG Fast Tracks

PCI Express® 5.0 Specification Progress Update: Version 0.7 Released to Members By Al Yanes, PCI-SIG President and Chairman After successfully releasing PCIe® 4.0 Specification Version 1.0 last October, the members of the PCI-

Embedded PCI Express Graphics Advantech

Doubling Bandwidth in Under Two Years PCI Express Base

Hot Chips 2017 PCI Express 4.0 Standard Coming In 2017

PCI Express® 4.0 Interposer For Summit™ T416 The Gen4 Interposer supports data rates of 2.5, 5.0, 8.0, and 16.0 GT/s, and is available in three configurations: x1, x4, x8 and x16. Each configuration supports lesser link widths (e.g., the x4 configuration supports x4, x2 and x1 through the x4 PCIe connector mounted on the card, but cannot support greater than x4 since the host slot connector

Embedded PCI Express Graphics Advantech

PCI Express 4.0 is done 5.0 spec nears approval Network

Characterization and Production Testing At 3.2-5.0 GB/s

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

PCI Express PIPE Overview MindShare

PCIe 5.0 To Be Finalized In 2019 PCI-SIG Fast Tracks

Doubling Bandwidth in Under Two Years PCI Express Base

PCI-SIG also teased the upcoming PCIe 5.0 specification. Penciled in for 2019, PCIe 5.0 will push the available bandwidth to 32 GT/s. One application that the consortium has in mind is high-end

Pci express external cabling 1 0 specification pdf

USB 2.0 5-Port PCI Express Card Belkin – iPhone iWatch

PCI Express is scalable, as well. PCIe 4.0 can be implemented as one lane up through sixteen bidirectional lanes, at almost 16 GT/s. Each lane is a differential pair comprised of one transmit signal and one receive signal.

PCI Express PIPE Overview MindShare

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

PCIe 4.0 specification finally out with 16 GT/s on tap

PCI-SIG Previews 32GT/s PCIe 5.0 Spec Releases PCI

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs. The primary differences between a PCI Express add-in card (as defined by the PCI Express Card Electromechanical Specification) and a PCI Express Mini Card add-in card is a …

PCI Express Label Specification and Usage Guidelines

Pci express external cabling 1 0 specification pdf

EN Congratulations and thank you for purchasing the new USB 2.0 5-Port PCI Express Card (the Card) from Belkin. The Card is designed to take advantage of the additional

PCIe 5.0 To Be Finalized In 2019 PCI-SIG Fast Tracks

PCI Express Label Specification and Usage Guidelines

PCI-SIG Fast Tracks Evolution to 32GT/s with PCI Express 5

PCI Express External Cabling 1. 0 Specification 2MB PDF.PCI Express: Performance Scalability for the Next Decade. PCI-SIG Delivers PCI Express Bridge 1. 0 Specification.Retrieved 2010-10-18. 0 final draft spec published.

PCI Express Label Specification and Usage Guidelines

PCI-Express 4.0 specification tomshardware.com

PCI-Express Base Specification and USB 3.0 Specification shall supersede the PIPE spec. This spec provides some information about how the MAC could use the PIPE interface for various LTSSM states and Link states.

Embedded PCI Express Graphics Advantech

PCI EXPRESS LABEL SPECIFICATION AND USAGE GUIDELINES, REV. 1.0 5 Objective of the Specification The purpose of this document is to clarify and standardize how PCI …

PCI Express 4.0 Spec Has Been Finalized PCIe 5.0 to go

PCI Express 4.0 Test Solution (QPHY-PCIE4-TX-RX) Datasheet

PCI Express® 5.0 Specification Progress Update Version 0

February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0 approved in July 2002 PCI Express ¾Formerly known as 3GIO ¾Version 1.0 approved in July 2002. February …

PCI-Express 4.0 specification tomshardware.com

PCI-SIG Fast Tracks Evolution to 32GT/s with PCI Express 5

PCI Express® 4.0 Interposer For Summit™ T416 The Gen4 Interposer supports data rates of 2.5, 5.0, 8.0, and 16.0 GT/s, and is available in three configurations: x1, x4, x8 and x16. Each configuration supports lesser link widths (e.g., the x4 configuration supports x4, x2 and x1 through the x4 PCIe connector mounted on the card, but cannot support greater than x4 since the host slot connector

PCI Express 4.0 Test Solution (QPHY-PCIE4-TX-RX) Datasheet

PEX8605 PCI Express Gen 2 Switch 4 Lanes 4 Ports

PCI-Express 4.0 specification tomshardware.com

Quickly test your Design to the PCIe® Base and CEM Specifications Overview. Supports PCIe® 4.0 (16GT/s and 8GT/s) PCIe® 5.0 Supported through “Extended Protection”

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

USB 2.0 5-Port PCI Express Card Belkin – iPhone iWatch

The group just announced PCI Express 5.0 has entered the 0.3 release phase of development. Next comes 0.7 and then 1.0, the finalized specification released to manufacturers. Sources say the final

PCIe 5.0 To Be Finalized In 2019 PCI-SIG Fast Tracks

Our PCI-SIG ® members have been hard at work. In 2017, we delivered PCI Express ® 4.0 with its 16 GT/s, while also diving headfirst into PCI Express 5.0 development – first announced at our annual PCI-SIG DevCon in June 2017.

PCI-Express 4.0 specification tomshardware.com

PCI Express 4.0 is done 5.0 spec nears approval Network

PCI Express External Cabling 1. 0 Specification 2MB PDF.PCI Express: Performance Scalability for the Next Decade. PCI-SIG Delivers PCI Express Bridge 1. 0 Specification.Retrieved 2010-10-18. 0 final draft spec published.

Hot Chips 2017 PCI Express 4.0 Standard Coming In 2017

Doubling Bandwidth in Under Two Years PCI Express Base

phy interface for pci express, sata, usb 3.1, displayport, and converged io architectures, intellectual property disclaimer . this specification is provided “as is” with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. a copyright license is hereby

PCI Express 4.0 Spec Has Been Finalized PCIe 5.0 to go

PCI Express PIPE Overview MindShare

PCI-Express 4.0 specification tomshardware.com

PCI Express is scalable, as well. PCIe 4.0 can be implemented as one lane up through sixteen bidirectional lanes, at almost 16 GT/s. Each lane is a differential pair comprised of one transmit signal and one receive signal.

PCI-SIG Fast Tracks Evolution to 32GT/s with PCI Express 5

PCI Express 4.0 is done 5.0 spec nears approval Network

16.0 G 0.5 ps RMS 3.2 PCI-Express 4.0 Independent Refclk Requirements Currently the PCI-Express 4.0 specification does not define the jitter transfer function and jitter limits for the Independent Refclk archi-tecture. Instead, the approach taken is to allow the implementation and associated reference clock jitter and transfer function trade-offs that impact the overall transmitter jitter to

2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater w

PHY Interface for the PCI Express Architecture applistar.com

The PEX8605 is designed to be fully compliant with the PCI Express Base Specification r2.1 and is backwards compatible to PCI Express Base Specification r1.1 and r1.0a.

Version 5.0 2007 PEX 8114 Broadcom Limited

PCI-SIG has released the PCIe 4.0 Specification Version 1.0 for review and it is available for download on their website. The final published spec describes the PCI Express architecture

Doubling Bandwidth in Under Two Years PCI Express Base

PCI-SIG Previews 32GT/s PCIe 5.0 Spec Releases PCI