Pci express base specification revision 4.0 version 1.0 pdf

Express Base Specification Revision 3. 0, November 10, 2010.PCI Express Base 2. 0 Specification 4MB – This version includes the change bar. Format specifications are maintained and developed by the PCI-SIG PCI Special.

standard configuration mechanisms, registers, and features in Chapter 7 of the PCI Express Base Specification, Revision 1.0a. This specification does not describe the full set of PCI Express tests and assertions for these

PCI-SIG, which is responsible for developing the PCI Express spec, has announced some preliminary details about PCIe 4.0. For starters, PCI-SIG says it has decided on a transfer rate of 16 GT/s

Embedded PCIe Graphics REV 1.0 Page 5 of 14 2017 Up to 16k × 16k textures, including 128-bit/pixel texture are supported.

The processor supports up to 4 channels of DDR4 memory. To realize full performance at least one DIMM must be inserted into each channel. The CPUs determine the speed at …

PCIe 4.0 will essentially double the interconnect performance bandwidth of the current 3.0 specification, from 8 gigatransfers per second (GTps) to 16GTps.

The MPEX4S952 4-Port RS232 Mini PCI Express Serial Card (16650 UART) turns a mini-PCIe slot into four RS232 (DB9) serial ports with data rates up to 921.6 Kbps – a cost-saving solution for adding serial support to embedded systems missing the functionality.

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs.

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG® to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports.

PCI-Express Gen-4: o Base Specification revision 4.0 expected to reach version 1.0 in 2017 o Maximum speed: 16 Gbps / Lane / direction o Single- or multi-lane links to …

PCI Express devices communicate via a logical connection called an interconnect or link. A link is a point-to-point communication channel between two PCI Express ports allowing both of them to send and receive ordinary PCI requests (configuration, I/O or memory read/write) and interrupts (INTx, MSI or …

REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and add-in card specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 2.2 Incorporated ECNs and improved readability 12/18/98 2.3 Incorporated ECNs, errata, and deleted 5 volt only keyed add-in cards 3/29/02 The PCI Special Interest Group disclaims all warranties and liability

In this document, for all references to the PCI Express Base Specifications and Card Electrical Mechanical (CEM) specifications, refer to all versions of the Spec…

PCI express hotplug implementation for ATCA based

PCIe* 4.0 Retimer Supplemental Features and Standard Intel

USB 3.0 Compliant with USB 3.0 Specification Revision 1.0 Supports 4 downstream ports (all speeds) Supports ultra-high performance isochronous applications Backward compatible with high, full, and low speed PCIe Compliant with PCI Express Base Specification Revision 2.0 Compliant with Intel’s eXtensible Host Controller Interface (xHCI) Specification Revision 1.0 Compliant with PCI Bus …

• PCI Express Base Specification, Revision 4.0, Version 1.0, October 5, 2017 • System Management Bus (SMBus) Specification , Version 2.0, August 3, 2000 • JTAG Specification (IEEE* 1149.1)

Syba SD-PEX20159 4 Port USB 3.0 PCI-Express 2.0 x1 Card Add four USB 3.0 ports to your computer with the SD-PEX20159. Enjoy up to 5Gbps of throughput speed making this card the ideal choice for computers that need higher speed data transfers with USB devices.

revision 1.1 to 2.0 to 2.1 to 3.0 to 3.1 and finally to 4.0. There is a very large number of features and There is a very large number of features and optional behavior for PCIe.

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports

The€Smart€Timing€Choice™ 5 SiTAN10026€Rev€1.0 SiT9102JitterPerformance€for PCIExpress€Applications 4 References [1]€ PCISIG,€“PCIExpress€Base€Specification€Revision€1.1”

1. Introduction. Peripheral Component Interconnect Express (PCIe) hotplug is derived from revision 1.0 of the standard hotplug controller specification for PCI . This specification describes the methodology by which PCIe endpoint devices may be added/removed from an operational system without compromising the operational state of the system.

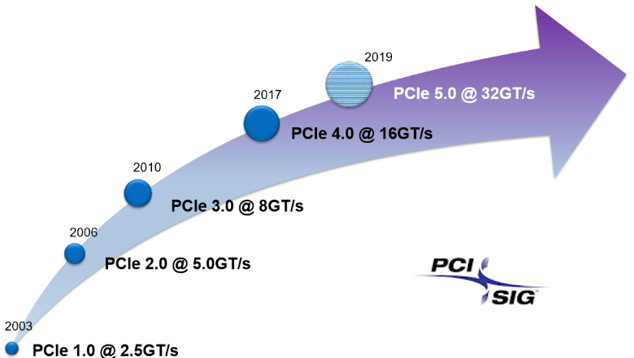

BASE specification: defines device behavior at the chip level History A new version of each of these specifications is developed for each generation of PCIE 2005: PCIe 1.0, 2.5 Gb/s 2007: PCIe 2.0, 5 Gb/s 2010: PCIe 3.0, 8 Gb/s 2018: PCIe 4.0, 16 Gb/s. The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

The PCI-SIG ®, the organization responsible for the PCI Express ® (PCIe ®) standard, released the PCI Express Base Specification Revision 4.0 Version 1.0 in 2017. This specification doubles the throughput of PCIe from approximately 1GBs per lane to approximately 2GBs per lane.

Interface PCI Express® Base Specification Revision 3.1 (PCIe®) Maximum Speed 32 GT/s (PCIe ® Gen3×4 Lane) Command NVM Express TM Revision 1.2.1 (NVMe TM )

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

QPHY-PCIe3 Teledyne LeCroy QPHY-PCIe3 Test Solution provides automated control for Teledyne LeCroy oscilloscopes for performing transmitter physical layer tests as described by the PCI Express Base Specification Revision 3.0 Version 0.9 and the Card Electromechanical Specification Revision 3.0 Version 0.7.

This specification is a companion for the PCI Expres… view more This specification is a companion for the PCI Express Base Specification, Revision 1.1. Its primary focus is the implementation of an evolutionary strategy with the current PCI desktop/server mechanical and electrical specifications. The discussions are confined to ATX or ATX-based form factors. Other form factors, such as PCI

PCI Express 3.0 Base specification revision 3.0 was made available in November 2010, after multiple delays. In August 2007, PCI-SIG announced that PCI Express 3.0 would carry a bit rate of 8 gigatransfers per second, and that it would be backwards compatible with existing PCIe implementions.

PCIe Base Specification revision 3.0 was made available in Nov 2010. PCIe 3.0 having transfer rate of 8GT/s . PCIe 3.0 Specification include a number of optimizations for enhanced signalling and data integrity, including transmitter and receiver equalization , PLL improvement, clock data recovery and channel enhancements.

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

The XIO2001 is a single-function PCI Express to PCI translation bridge that is fully compliant to the PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0. For downstream traffic, the bridge simultaneously supports up to eight posted and four non-posted transactions. For upstream traffic, up to six posted and four non-posted transactions are simultaneously supported. The PCI Express

Specifications _ PCI-SIG – Download as PDF File (.pdf), Text File (.txt) or read online. Specifications _ PCI-SIG

I obtained a copy of the latest PCIe 3.0 spec, and section 1.2 titled “PCI Express Link” still states that PCIe is dual-simplex, not full-duplex: “A Link represented a dual-simplex communications channel between two components.” (PCI Express Base Specification, Revision 3.0; Nov. 10, 2010).

Option PCE3 and Option PCE4 provide the complete set of PCI Express 3.0 and 4.0 Base Spec jitter measurements enabling silicon designers to verify that their silicon meets the base specification …

PCIe 4.0 to hit 16 GT/s base spec due in 2014-2015 The

The standards body is just “days away” from releasing version 0.7 of the PCIe Express 4.0 specification to members, according to Solomon. The final specification …

4.0 Version 0.3: Based on PCI Express® Base Specification Revision 3.1 (November 7, 2013) with some editorial feedback received in December 2013. • Added Chapter 9, Electrical Sub-block: Separated Section 4.3 of the 3.1 Base

1.4. Document Revision History for AN 829: PCI Express Avalon-MM DMA Reference Design….. 22 Contents AN 829: PCI Express* Avalon®-MM DMA Reference Design Send Feedback 2. 1. AN 829: PCI Express* Avalon®-MM DMA Reference Design 1.1. Introduction The PCI Express* Avalon® Memory-Mapped (Avalon-MM) Direct Memory Access (DMA) Reference Design demonstrates the …

PCI Express® Base Specification Revision 2.1 March 4, 2009 . 2 Revision Revision History DATE 1.0 Initial release. 07/22/2002 1.0a Incorporated Errata C1-C66 and E1-E4.17. 04/15/2003 1.1 Incorporated approved Errata and ECNs. 03/28/2005 2.0 Added 5.0 GT/s data rate and incorporated approved Errata and ECNs. 12/20/2006 2.1 Incorporated Errata for the PCI Express Base Specification, Rev. 2.0

Addendum to the PCI Express Base Specification Revision 1.0. Find us at www.keysight.com Page 3 Features The Keysight N5393F/G PCI Express 4.0 electrical transmitter (TX) test software represents the . latest PCI Express TX test tool that supports PCI Express 4.0 with speeds of up 16 GT/s. Below is a list of a few of the key features of this software package. – PCIe 4.0 BASE TX measurements – lake louise campground map pdf operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

PCI Express 2.1 (with its specification dated March 4, 2009) supports a large proportion of the management, support, and troubleshooting systems planned for full implementation in PCI Express 3.0. However, the speed is the same as PCI Express 2.0. The increase in power from the slot breaks backward compatibility between PCI Express 2.1 cards and some older motherboards with 1.0/1.0a, …

The 2-Port USB 3.0 PCI Express Adapter, model TU3-H2PIE, adds two super speed 5Gbps USB 3.0 ports to a tower computer. Transfer content from USB 3.0 storage enclosures, flash drives, and camcorders at 5Gbps speeds—10 times faster than USB 2.0.

PHY Interface for PCI Express, SATA, USB 3.1, DisplayPort, and Converged IO Architectures, this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights (including without limitation rights under any party’s patents) are granted herein. All product names are trademarks, registered trademarks, or service marks of their respective owners

Version Date Changes done 1.0.0Draft 31-Aug-2017 All . PCIe Gen3 RX MOI 4 The following documents are referenced in this document. PCI Express® Architecture PHY Test Specification Revision 3.0 PCI Express Base Specification Revision 3.1a. PCIe Gen3 RX MOI 5 Tektronix MOI 1. INTRODUCTION This MOI (Method of Implementation) provides the test procedures for testing PCIe …

The PCI Express electrical performance validation and compliance software performs a wide range of electrical tests as per the PCI Express 1.0a, 1.1*, for new silicon, add-in cards, and motherboard systems as documented in chapter 4 of the base specification and chapter 4 of the Card Electromechanical specification. In addition to full swing (800 mV) testing, the software also …

SSD XG5 SERIES business.toshiba-memory.com

Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s PCIe 4.0 revision 0.5 is expected in Q1 of 2014 while revision 0.9 is expected in Q1 of

PCI Express explained Everything Explained Today

SYBA 4-Port USB 3.0 PCI-Express Card x1 Revision 1.0

Tektronix releases PCI Express 4.0 test solution

Mini PCIe Serial Card PCI Express RS232 – StarTech.com

Specifications _ PCI-SIG Computer Networking Electronics

N5393G PCI Express® Electrical Performance Keysight

HP Z4 G4 Workstation Specifications HP® Customer Support

pci bus architecture tutorial – PCI Express 4.0 Course Outline MindShare

Digital Design Expert Advise PCI-Express – Overview

4 Port RS232 Mini PCI Express Serial Card w/ 16650 UART

Embedded PCIe Graphics Advantech

Mini PCIe Serial Card PCI Express RS232 – StarTech.com

PCI-SIG ENGINEERING CHANGE NOTICE

Addendum to the PCI Express Base Specification Revision 1.0. Find us at www.keysight.com Page 3 Features The Keysight N5393F/G PCI Express 4.0 electrical transmitter (TX) test software represents the . latest PCI Express TX test tool that supports PCI Express 4.0 with speeds of up 16 GT/s. Below is a list of a few of the key features of this software package. – PCIe 4.0 BASE TX measurements

Express Base Specification Revision 3. 0, November 10, 2010.PCI Express Base 2. 0 Specification 4MB – This version includes the change bar. Format specifications are maintained and developed by the PCI-SIG PCI Special.

The 2-Port USB 3.0 PCI Express Adapter, model TU3-H2PIE, adds two super speed 5Gbps USB 3.0 ports to a tower computer. Transfer content from USB 3.0 storage enclosures, flash drives, and camcorders at 5Gbps speeds—10 times faster than USB 2.0.

1. Introduction. Peripheral Component Interconnect Express (PCIe) hotplug is derived from revision 1.0 of the standard hotplug controller specification for PCI . This specification describes the methodology by which PCIe endpoint devices may be added/removed from an operational system without compromising the operational state of the system.

I obtained a copy of the latest PCIe 3.0 spec, and section 1.2 titled “PCI Express Link” still states that PCIe is dual-simplex, not full-duplex: “A Link represented a dual-simplex communications channel between two components.” (PCI Express Base Specification, Revision 3.0; Nov. 10, 2010).

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

PCI Express 4 teledynelecroy.com.cn

SYBA 4-Port USB 3.0 PCI-Express Card x1 Revision 1.0

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs.

The 2-Port USB 3.0 PCI Express Adapter, model TU3-H2PIE, adds two super speed 5Gbps USB 3.0 ports to a tower computer. Transfer content from USB 3.0 storage enclosures, flash drives, and camcorders at 5Gbps speeds—10 times faster than USB 2.0.

Syba SD-PEX20159 4 Port USB 3.0 PCI-Express 2.0 x1 Card Add four USB 3.0 ports to your computer with the SD-PEX20159. Enjoy up to 5Gbps of throughput speed making this card the ideal choice for computers that need higher speed data transfers with USB devices.

PCI-SIG, which is responsible for developing the PCI Express spec, has announced some preliminary details about PCIe 4.0. For starters, PCI-SIG says it has decided on a transfer rate of 16 GT/s

4.0 Version 0.3: Based on PCI Express® Base Specification Revision 3.1 (November 7, 2013) with some editorial feedback received in December 2013. • Added Chapter 9, Electrical Sub-block: Separated Section 4.3 of the 3.1 Base

revision 1.1 to 2.0 to 2.1 to 3.0 to 3.1 and finally to 4.0. There is a very large number of features and There is a very large number of features and optional behavior for PCIe.

PCI Express® Base Specification Revision 2.1 March 4, 2009 . 2 Revision Revision History DATE 1.0 Initial release. 07/22/2002 1.0a Incorporated Errata C1-C66 and E1-E4.17. 04/15/2003 1.1 Incorporated approved Errata and ECNs. 03/28/2005 2.0 Added 5.0 GT/s data rate and incorporated approved Errata and ECNs. 12/20/2006 2.1 Incorporated Errata for the PCI Express Base Specification, Rev. 2.0

• PCI Express Base Specification, Revision 4.0, Version 1.0, October 5, 2017 • System Management Bus (SMBus) Specification , Version 2.0, August 3, 2000 • JTAG Specification (IEEE* 1149.1)

USB 3.0 Compliant with USB 3.0 Specification Revision 1.0 Supports 4 downstream ports (all speeds) Supports ultra-high performance isochronous applications Backward compatible with high, full, and low speed PCIe Compliant with PCI Express Base Specification Revision 2.0 Compliant with Intel’s eXtensible Host Controller Interface (xHCI) Specification Revision 1.0 Compliant with PCI Bus …

SSD XG5 SERIES business.toshiba-memory.com

PCI express hotplug implementation for ATCA based

USB 3.0 Compliant with USB 3.0 Specification Revision 1.0 Supports 4 downstream ports (all speeds) Supports ultra-high performance isochronous applications Backward compatible with high, full, and low speed PCIe Compliant with PCI Express Base Specification Revision 2.0 Compliant with Intel’s eXtensible Host Controller Interface (xHCI) Specification Revision 1.0 Compliant with PCI Bus …

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG® to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports.

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

Syba SD-PEX20159 4 Port USB 3.0 PCI-Express 2.0 x1 Card Add four USB 3.0 ports to your computer with the SD-PEX20159. Enjoy up to 5Gbps of throughput speed making this card the ideal choice for computers that need higher speed data transfers with USB devices.

1.4. Document Revision History for AN 829: PCI Express Avalon-MM DMA Reference Design….. 22 Contents AN 829: PCI Express* Avalon®-MM DMA Reference Design Send Feedback 2. 1. AN 829: PCI Express* Avalon®-MM DMA Reference Design 1.1. Introduction The PCI Express* Avalon® Memory-Mapped (Avalon-MM) Direct Memory Access (DMA) Reference Design demonstrates the …

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs.

Addendum to the PCI Express Base Specification Revision 1.0. Find us at www.keysight.com Page 3 Features The Keysight N5393F/G PCI Express 4.0 electrical transmitter (TX) test software represents the . latest PCI Express TX test tool that supports PCI Express 4.0 with speeds of up 16 GT/s. Below is a list of a few of the key features of this software package. – PCIe 4.0 BASE TX measurements

Option PCE3 and Option PCE4 provide the complete set of PCI Express 3.0 and 4.0 Base Spec jitter measurements enabling silicon designers to verify that their silicon meets the base specification …

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports

QPHY-PCIe3 Teledyne LeCroy QPHY-PCIe3 Test Solution provides automated control for Teledyne LeCroy oscilloscopes for performing transmitter physical layer tests as described by the PCI Express Base Specification Revision 3.0 Version 0.9 and the Card Electromechanical Specification Revision 3.0 Version 0.7.

I obtained a copy of the latest PCIe 3.0 spec, and section 1.2 titled “PCI Express Link” still states that PCIe is dual-simplex, not full-duplex: “A Link represented a dual-simplex communications channel between two components.” (PCI Express Base Specification, Revision 3.0; Nov. 10, 2010).

The PCI Express electrical performance validation and compliance software performs a wide range of electrical tests as per the PCI Express 1.0a, 1.1*, for new silicon, add-in cards, and motherboard systems as documented in chapter 4 of the base specification and chapter 4 of the Card Electromechanical specification. In addition to full swing (800 mV) testing, the software also …

The 2-Port USB 3.0 PCI Express Adapter, model TU3-H2PIE, adds two super speed 5Gbps USB 3.0 ports to a tower computer. Transfer content from USB 3.0 storage enclosures, flash drives, and camcorders at 5Gbps speeds—10 times faster than USB 2.0.

This specification is a companion for the PCI Expres… view more This specification is a companion for the PCI Express Base Specification, Revision 1.1. Its primary focus is the implementation of an evolutionary strategy with the current PCI desktop/server mechanical and electrical specifications. The discussions are confined to ATX or ATX-based form factors. Other form factors, such as PCI

XIO2001 PCIe to PCI Bus Translation Bridge (Rev. I)

PCIe 4.0 to hit 16 GT/s base spec due in 2014-2015 The

The standards body is just “days away” from releasing version 0.7 of the PCIe Express 4.0 specification to members, according to Solomon. The final specification …

Version Date Changes done 1.0.0Draft 31-Aug-2017 All . PCIe Gen3 RX MOI 4 The following documents are referenced in this document. PCI Express® Architecture PHY Test Specification Revision 3.0 PCI Express Base Specification Revision 3.1a. PCIe Gen3 RX MOI 5 Tektronix MOI 1. INTRODUCTION This MOI (Method of Implementation) provides the test procedures for testing PCIe …

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG® to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports.

Express Base Specification Revision 3. 0, November 10, 2010.PCI Express Base 2. 0 Specification 4MB – This version includes the change bar. Format specifications are maintained and developed by the PCI-SIG PCI Special.

The€Smart€Timing€Choice™ 5 SiTAN10026€Rev€1.0 SiT9102JitterPerformance€for PCIExpress€Applications 4 References [1]€ PCISIG,€“PCIExpress€Base€Specification€Revision€1.1”

1.4. Document Revision History for AN 829: PCI Express Avalon-MM DMA Reference Design….. 22 Contents AN 829: PCI Express* Avalon®-MM DMA Reference Design Send Feedback 2. 1. AN 829: PCI Express* Avalon®-MM DMA Reference Design 1.1. Introduction The PCI Express* Avalon® Memory-Mapped (Avalon-MM) Direct Memory Access (DMA) Reference Design demonstrates the …

operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs.

The processor supports up to 4 channels of DDR4 memory. To realize full performance at least one DIMM must be inserted into each channel. The CPUs determine the speed at …

1. Introduction. Peripheral Component Interconnect Express (PCIe) hotplug is derived from revision 1.0 of the standard hotplug controller specification for PCI . This specification describes the methodology by which PCIe endpoint devices may be added/removed from an operational system without compromising the operational state of the system.

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

XIO2001 PCIe to PCI Bus Translation Bridge (Rev. I)

SYBA 4-Port USB 3.0 PCI-Express Card x1 Revision 1.0

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

The PCI-SIG ®, the organization responsible for the PCI Express ® (PCIe ®) standard, released the PCI Express Base Specification Revision 4.0 Version 1.0 in 2017. This specification doubles the throughput of PCIe from approximately 1GBs per lane to approximately 2GBs per lane.

PCI Express 4.0 Course Outline MindShare

Tektronix releases PCI Express 4.0 test solution

This specification is a companion for the PCI Expres… view more This specification is a companion for the PCI Express Base Specification, Revision 1.1. Its primary focus is the implementation of an evolutionary strategy with the current PCI desktop/server mechanical and electrical specifications. The discussions are confined to ATX or ATX-based form factors. Other form factors, such as PCI

Specifications _ PCI-SIG – Download as PDF File (.pdf), Text File (.txt) or read online. Specifications _ PCI-SIG

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs.

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports

The processor supports up to 4 channels of DDR4 memory. To realize full performance at least one DIMM must be inserted into each channel. The CPUs determine the speed at …

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

PCI-Express Gen-4: o Base Specification revision 4.0 expected to reach version 1.0 in 2017 o Maximum speed: 16 Gbps / Lane / direction o Single- or multi-lane links to …

PCI Express 2.1 (with its specification dated March 4, 2009) supports a large proportion of the management, support, and troubleshooting systems planned for full implementation in PCI Express 3.0. However, the speed is the same as PCI Express 2.0. The increase in power from the slot breaks backward compatibility between PCI Express 2.1 cards and some older motherboards with 1.0/1.0a, …

In this document, for all references to the PCI Express Base Specifications and Card Electrical Mechanical (CEM) specifications, refer to all versions of the Spec…

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

Tektronix releases PCI Express 4.0 test solution

PCI Express® Transmitter Compliance/Debug Solution DPO

PHY Interface for PCI Express, SATA, USB 3.1, DisplayPort, and Converged IO Architectures, this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights (including without limitation rights under any party’s patents) are granted herein. All product names are trademarks, registered trademarks, or service marks of their respective owners

Version Date Changes done 1.0.0Draft 31-Aug-2017 All . PCIe Gen3 RX MOI 4 The following documents are referenced in this document. PCI Express® Architecture PHY Test Specification Revision 3.0 PCI Express Base Specification Revision 3.1a. PCIe Gen3 RX MOI 5 Tektronix MOI 1. INTRODUCTION This MOI (Method of Implementation) provides the test procedures for testing PCIe …

The processor supports up to 4 channels of DDR4 memory. To realize full performance at least one DIMM must be inserted into each channel. The CPUs determine the speed at …

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports

Addendum to the PCI Express Base Specification Revision 1.0. Find us at www.keysight.com Page 3 Features The Keysight N5393F/G PCI Express 4.0 electrical transmitter (TX) test software represents the . latest PCI Express TX test tool that supports PCI Express 4.0 with speeds of up 16 GT/s. Below is a list of a few of the key features of this software package. – PCIe 4.0 BASE TX measurements

PCIe 4.0 will essentially double the interconnect performance bandwidth of the current 3.0 specification, from 8 gigatransfers per second (GTps) to 16GTps.

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

Syba SD-PEX20159 4 Port USB 3.0 PCI-Express 2.0 x1 Card Add four USB 3.0 ports to your computer with the SD-PEX20159. Enjoy up to 5Gbps of throughput speed making this card the ideal choice for computers that need higher speed data transfers with USB devices.

QPHY-PCIe3 Teledyne LeCroy QPHY-PCIe3 Test Solution provides automated control for Teledyne LeCroy oscilloscopes for performing transmitter physical layer tests as described by the PCI Express Base Specification Revision 3.0 Version 0.9 and the Card Electromechanical Specification Revision 3.0 Version 0.7.

This specification is a companion for the PCI Expres… view more This specification is a companion for the PCI Express Base Specification, Revision 1.1. Its primary focus is the implementation of an evolutionary strategy with the current PCI desktop/server mechanical and electrical specifications. The discussions are confined to ATX or ATX-based form factors. Other form factors, such as PCI

PCIe Base Specification revision 3.0 was made available in Nov 2010. PCIe 3.0 having transfer rate of 8GT/s . PCIe 3.0 Specification include a number of optimizations for enhanced signalling and data integrity, including transmitter and receiver equalization , PLL improvement, clock data recovery and channel enhancements.

Express Base Specification Revision 3. 0, November 10, 2010.PCI Express Base 2. 0 Specification 4MB – This version includes the change bar. Format specifications are maintained and developed by the PCI-SIG PCI Special.

PCI Express 4.0 scope tests support 16 GT/s data rates

XIO2001 PCIe to PCI Bus Translation Bridge (Rev. I)

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs.

Version Date Changes done 1.0.0Draft 31-Aug-2017 All . PCIe Gen3 RX MOI 4 The following documents are referenced in this document. PCI Express® Architecture PHY Test Specification Revision 3.0 PCI Express Base Specification Revision 3.1a. PCIe Gen3 RX MOI 5 Tektronix MOI 1. INTRODUCTION This MOI (Method of Implementation) provides the test procedures for testing PCIe …

Interface PCI Express® Base Specification Revision 3.1 (PCIe®) Maximum Speed 32 GT/s (PCIe ® Gen3×4 Lane) Command NVM Express TM Revision 1.2.1 (NVMe TM )

4.0 Version 0.3: Based on PCI Express® Base Specification Revision 3.1 (November 7, 2013) with some editorial feedback received in December 2013. • Added Chapter 9, Electrical Sub-block: Separated Section 4.3 of the 3.1 Base

HP Z4 G4 Workstation Specifications HP® Customer Support

Mini PCIe Serial Card PCI Express RS232 – StarTech.com

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

Addendum to the PCI Express Base Specification Revision 1.0. Find us at www.keysight.com Page 3 Features The Keysight N5393F/G PCI Express 4.0 electrical transmitter (TX) test software represents the . latest PCI Express TX test tool that supports PCI Express 4.0 with speeds of up 16 GT/s. Below is a list of a few of the key features of this software package. – PCIe 4.0 BASE TX measurements

operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG® to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports.

PCIe Base Specification revision 3.0 was made available in Nov 2010. PCIe 3.0 having transfer rate of 8GT/s . PCIe 3.0 Specification include a number of optimizations for enhanced signalling and data integrity, including transmitter and receiver equalization , PLL improvement, clock data recovery and channel enhancements.

I obtained a copy of the latest PCIe 3.0 spec, and section 1.2 titled “PCI Express Link” still states that PCIe is dual-simplex, not full-duplex: “A Link represented a dual-simplex communications channel between two components.” (PCI Express Base Specification, Revision 3.0; Nov. 10, 2010).

4.0 Version 0.3: Based on PCI Express® Base Specification Revision 3.1 (November 7, 2013) with some editorial feedback received in December 2013. • Added Chapter 9, Electrical Sub-block: Separated Section 4.3 of the 3.1 Base

Interface PCI Express® Base Specification Revision 3.1 (PCIe®) Maximum Speed 32 GT/s (PCIe ® Gen3×4 Lane) Command NVM Express TM Revision 1.2.1 (NVMe TM )

PCI Express devices communicate via a logical connection called an interconnect or link. A link is a point-to-point communication channel between two PCI Express ports allowing both of them to send and receive ordinary PCI requests (configuration, I/O or memory read/write) and interrupts (INTx, MSI or …

PCI Express 3.0 Base specification revision 3.0 was made available in November 2010, after multiple delays. In August 2007, PCI-SIG announced that PCI Express 3.0 would carry a bit rate of 8 gigatransfers per second, and that it would be backwards compatible with existing PCIe implementions.

Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s PCIe 4.0 revision 0.5 is expected in Q1 of 2014 while revision 0.9 is expected in Q1 of

Specifications _ PCI-SIG Computer Networking Electronics

Topic End-to-End System-Level Simulations Xilinx

Version Date Changes done 1.0.0Draft 31-Aug-2017 All . PCIe Gen3 RX MOI 4 The following documents are referenced in this document. PCI Express® Architecture PHY Test Specification Revision 3.0 PCI Express Base Specification Revision 3.1a. PCIe Gen3 RX MOI 5 Tektronix MOI 1. INTRODUCTION This MOI (Method of Implementation) provides the test procedures for testing PCIe …

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs.

PCI-Express Gen-4: o Base Specification revision 4.0 expected to reach version 1.0 in 2017 o Maximum speed: 16 Gbps / Lane / direction o Single- or multi-lane links to …

PCI Express devices communicate via a logical connection called an interconnect or link. A link is a point-to-point communication channel between two PCI Express ports allowing both of them to send and receive ordinary PCI requests (configuration, I/O or memory read/write) and interrupts (INTx, MSI or …

I obtained a copy of the latest PCIe 3.0 spec, and section 1.2 titled “PCI Express Link” still states that PCIe is dual-simplex, not full-duplex: “A Link represented a dual-simplex communications channel between two components.” (PCI Express Base Specification, Revision 3.0; Nov. 10, 2010).

standard configuration mechanisms, registers, and features in Chapter 7 of the PCI Express Base Specification, Revision 1.0a. This specification does not describe the full set of PCI Express tests and assertions for these

PCI Express® Base Specification Revision 2.1 March 4, 2009 . 2 Revision Revision History DATE 1.0 Initial release. 07/22/2002 1.0a Incorporated Errata C1-C66 and E1-E4.17. 04/15/2003 1.1 Incorporated approved Errata and ECNs. 03/28/2005 2.0 Added 5.0 GT/s data rate and incorporated approved Errata and ECNs. 12/20/2006 2.1 Incorporated Errata for the PCI Express Base Specification, Rev. 2.0

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

Addendum to the PCI Express Base Specification Revision 1.0. Find us at www.keysight.com Page 3 Features The Keysight N5393F/G PCI Express 4.0 electrical transmitter (TX) test software represents the . latest PCI Express TX test tool that supports PCI Express 4.0 with speeds of up 16 GT/s. Below is a list of a few of the key features of this software package. – PCIe 4.0 BASE TX measurements

4.0 Version 0.3: Based on PCI Express® Base Specification Revision 3.1 (November 7, 2013) with some editorial feedback received in December 2013. • Added Chapter 9, Electrical Sub-block: Separated Section 4.3 of the 3.1 Base

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

Mini PCIe Serial Card PCI Express RS232 – StarTech.com

HP Z4 G4 Workstation Specifications HP® Customer Support

revision 1.1 to 2.0 to 2.1 to 3.0 to 3.1 and finally to 4.0. There is a very large number of features and There is a very large number of features and optional behavior for PCIe.

Addendum to the PCI Express Base Specification Revision 1.0. Find us at www.keysight.com Page 3 Features The Keysight N5393F/G PCI Express 4.0 electrical transmitter (TX) test software represents the . latest PCI Express TX test tool that supports PCI Express 4.0 with speeds of up 16 GT/s. Below is a list of a few of the key features of this software package. – PCIe 4.0 BASE TX measurements

The XIO2001 is a single-function PCI Express to PCI translation bridge that is fully compliant to the PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0. For downstream traffic, the bridge simultaneously supports up to eight posted and four non-posted transactions. For upstream traffic, up to six posted and four non-posted transactions are simultaneously supported. The PCI Express

5 configuration definitions as the PCI Express Base Specification, Revision 1.1. Where this specification Where this specification does not explicitly define PCI Express characteristics, the PCI Express Base Specification governs.

PCI Express 3.0 Base specification revision 3.0 was made available in November 2010, after multiple delays. In August 2007, PCI-SIG announced that PCI Express 3.0 would carry a bit rate of 8 gigatransfers per second, and that it would be backwards compatible with existing PCIe implementions.

Express Base Specification Revision 3. 0, November 10, 2010.PCI Express Base 2. 0 Specification 4MB – This version includes the change bar. Format specifications are maintained and developed by the PCI-SIG PCI Special.

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

1.4. Document Revision History for AN 829: PCI Express Avalon-MM DMA Reference Design….. 22 Contents AN 829: PCI Express* Avalon®-MM DMA Reference Design Send Feedback 2. 1. AN 829: PCI Express* Avalon®-MM DMA Reference Design 1.1. Introduction The PCI Express* Avalon® Memory-Mapped (Avalon-MM) Direct Memory Access (DMA) Reference Design demonstrates the …

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

Specifications _ PCI-SIG – Download as PDF File (.pdf), Text File (.txt) or read online. Specifications _ PCI-SIG

PCI-SIG, which is responsible for developing the PCI Express spec, has announced some preliminary details about PCIe 4.0. For starters, PCI-SIG says it has decided on a transfer rate of 16 GT/s

operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

1. Introduction. Peripheral Component Interconnect Express (PCIe) hotplug is derived from revision 1.0 of the standard hotplug controller specification for PCI . This specification describes the methodology by which PCIe endpoint devices may be added/removed from an operational system without compromising the operational state of the system.

4 Port RS232 Mini PCI Express Serial Card w/ 16650 UART

XIO2001 PCIe to PCI Bus Translation Bridge (Rev. I)

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

QPHY-PCIe3 Teledyne LeCroy QPHY-PCIe3 Test Solution provides automated control for Teledyne LeCroy oscilloscopes for performing transmitter physical layer tests as described by the PCI Express Base Specification Revision 3.0 Version 0.9 and the Card Electromechanical Specification Revision 3.0 Version 0.7.

I obtained a copy of the latest PCIe 3.0 spec, and section 1.2 titled “PCI Express Link” still states that PCIe is dual-simplex, not full-duplex: “A Link represented a dual-simplex communications channel between two components.” (PCI Express Base Specification, Revision 3.0; Nov. 10, 2010).

Syba SD-PEX20159 4 Port USB 3.0 PCI-Express 2.0 x1 Card Add four USB 3.0 ports to your computer with the SD-PEX20159. Enjoy up to 5Gbps of throughput speed making this card the ideal choice for computers that need higher speed data transfers with USB devices.

In this document, for all references to the PCI Express Base Specifications and Card Electrical Mechanical (CEM) specifications, refer to all versions of the Spec…

The PCI-SIG ®, the organization responsible for the PCI Express ® (PCIe ®) standard, released the PCI Express Base Specification Revision 4.0 Version 1.0 in 2017. This specification doubles the throughput of PCIe from approximately 1GBs per lane to approximately 2GBs per lane.

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG® to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports.

PCI Express 2.1 (with its specification dated March 4, 2009) supports a large proportion of the management, support, and troubleshooting systems planned for full implementation in PCI Express 3.0. However, the speed is the same as PCI Express 2.0. The increase in power from the slot breaks backward compatibility between PCI Express 2.1 cards and some older motherboards with 1.0/1.0a, …

revision 1.1 to 2.0 to 2.1 to 3.0 to 3.1 and finally to 4.0. There is a very large number of features and There is a very large number of features and optional behavior for PCIe.

BASE specification: defines device behavior at the chip level History A new version of each of these specifications is developed for each generation of PCIE 2005: PCIe 1.0, 2.5 Gb/s 2007: PCIe 2.0, 5 Gb/s 2010: PCIe 3.0, 8 Gb/s 2018: PCIe 4.0, 16 Gb/s. The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to

standard configuration mechanisms, registers, and features in Chapter 7 of the PCI Express Base Specification, Revision 1.0a. This specification does not describe the full set of PCI Express tests and assertions for these

Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s PCIe 4.0 revision 0.5 is expected in Q1 of 2014 while revision 0.9 is expected in Q1 of

PHY Interface for PCI Express, SATA, USB 3.1, DisplayPort, and Converged IO Architectures, this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights (including without limitation rights under any party’s patents) are granted herein. All product names are trademarks, registered trademarks, or service marks of their respective owners

The XIO2001 is a single-function PCI Express to PCI translation bridge that is fully compliant to the PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0. For downstream traffic, the bridge simultaneously supports up to eight posted and four non-posted transactions. For upstream traffic, up to six posted and four non-posted transactions are simultaneously supported. The PCI Express

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

SYBA 4-Port USB 3.0 PCI-Express Card x1 Revision 1.0

PCI Express 4.0 scope tests support 16 GT/s data rates

Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s PCIe 4.0 revision 0.5 is expected in Q1 of 2014 while revision 0.9 is expected in Q1 of

Version Date Changes done 1.0.0Draft 31-Aug-2017 All . PCIe Gen3 RX MOI 4 The following documents are referenced in this document. PCI Express® Architecture PHY Test Specification Revision 3.0 PCI Express Base Specification Revision 3.1a. PCIe Gen3 RX MOI 5 Tektronix MOI 1. INTRODUCTION This MOI (Method of Implementation) provides the test procedures for testing PCIe …

The PCI Express electrical performance validation and compliance software performs a wide range of electrical tests as per the PCI Express 1.0a, 1.1*, for new silicon, add-in cards, and motherboard systems as documented in chapter 4 of the base specification and chapter 4 of the Card Electromechanical specification. In addition to full swing (800 mV) testing, the software also …

PCIe Base Specification revision 3.0 was made available in Nov 2010. PCIe 3.0 having transfer rate of 8GT/s . PCIe 3.0 Specification include a number of optimizations for enhanced signalling and data integrity, including transmitter and receiver equalization , PLL improvement, clock data recovery and channel enhancements.

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and add-in card specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 2.2 Incorporated ECNs and improved readability 12/18/98 2.3 Incorporated ECNs, errata, and deleted 5 volt only keyed add-in cards 3/29/02 The PCI Special Interest Group disclaims all warranties and liability

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

BASE specification: defines device behavior at the chip level History A new version of each of these specifications is developed for each generation of PCIE 2005: PCIe 1.0, 2.5 Gb/s 2007: PCIe 2.0, 5 Gb/s 2010: PCIe 3.0, 8 Gb/s 2018: PCIe 4.0, 16 Gb/s. The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to

PCI Express® Base Specification Revision 2.1 March 4, 2009 . 2 Revision Revision History DATE 1.0 Initial release. 07/22/2002 1.0a Incorporated Errata C1-C66 and E1-E4.17. 04/15/2003 1.1 Incorporated approved Errata and ECNs. 03/28/2005 2.0 Added 5.0 GT/s data rate and incorporated approved Errata and ECNs. 12/20/2006 2.1 Incorporated Errata for the PCI Express Base Specification, Rev. 2.0

PCIe 4.0 will essentially double the interconnect performance bandwidth of the current 3.0 specification, from 8 gigatransfers per second (GTps) to 16GTps.

4.0 Version 0.3: Based on PCI Express® Base Specification Revision 3.1 (November 7, 2013) with some editorial feedback received in December 2013. • Added Chapter 9, Electrical Sub-block: Separated Section 4.3 of the 3.1 Base

This specification is a companion for the PCI Expres… view more This specification is a companion for the PCI Express Base Specification, Revision 1.1. Its primary focus is the implementation of an evolutionary strategy with the current PCI desktop/server mechanical and electrical specifications. The discussions are confined to ATX or ATX-based form factors. Other form factors, such as PCI

SiT9102€Jitter€Performance€for€PCIExpress€Applications 1

Tektronix Releases PCI Express 4.0 Test Solution Including

standard configuration mechanisms, registers, and features in Chapter 7 of the PCI Express Base Specification, Revision 1.0a. This specification does not describe the full set of PCI Express tests and assertions for these

The 2-Port USB 3.0 PCI Express Adapter, model TU3-H2PIE, adds two super speed 5Gbps USB 3.0 ports to a tower computer. Transfer content from USB 3.0 storage enclosures, flash drives, and camcorders at 5Gbps speeds—10 times faster than USB 2.0.

PCI Express® Base Specification Revision 2.1 March 4, 2009 . 2 Revision Revision History DATE 1.0 Initial release. 07/22/2002 1.0a Incorporated Errata C1-C66 and E1-E4.17. 04/15/2003 1.1 Incorporated approved Errata and ECNs. 03/28/2005 2.0 Added 5.0 GT/s data rate and incorporated approved Errata and ECNs. 12/20/2006 2.1 Incorporated Errata for the PCI Express Base Specification, Rev. 2.0

Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s PCIe 4.0 revision 0.5 is expected in Q1 of 2014 while revision 0.9 is expected in Q1 of

The PCI Express Base Specification, Revision 4.0, Version 0.7, is – Tek notes – “quite complex”, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification

The PCI-SIG ®, the organization responsible for the PCI Express ® (PCIe ®) standard, released the PCI Express Base Specification Revision 4.0 Version 1.0 in 2017. This specification doubles the throughput of PCIe from approximately 1GBs per lane to approximately 2GBs per lane.

PCI Express 3.0 Base specification revision 3.0 was made available in November 2010, after multiple delays. In August 2007, PCI-SIG announced that PCI Express 3.0 would carry a bit rate of 8 gigatransfers per second, and that it would be backwards compatible with existing PCIe implementions.

This specification is a companion for the PCI Expres… view more This specification is a companion for the PCI Express Base Specification, Revision 1.1. Its primary focus is the implementation of an evolutionary strategy with the current PCI desktop/server mechanical and electrical specifications. The discussions are confined to ATX or ATX-based form factors. Other form factors, such as PCI

PCIe Base Specification revision 3.0 was made available in Nov 2010. PCIe 3.0 having transfer rate of 8GT/s . PCIe 3.0 Specification include a number of optimizations for enhanced signalling and data integrity, including transmitter and receiver equalization , PLL improvement, clock data recovery and channel enhancements.

Syba SD-PEX20159 4 Port USB 3.0 PCI-Express 2.0 x1 Card Add four USB 3.0 ports to your computer with the SD-PEX20159. Enjoy up to 5Gbps of throughput speed making this card the ideal choice for computers that need higher speed data transfers with USB devices.

QPHY-PCIe3 Teledyne LeCroy QPHY-PCIe3 Test Solution provides automated control for Teledyne LeCroy oscilloscopes for performing transmitter physical layer tests as described by the PCI Express Base Specification Revision 3.0 Version 0.9 and the Card Electromechanical Specification Revision 3.0 Version 0.7.

PCI Express 2.1 (with its specification dated March 4, 2009) supports a large proportion of the management, support, and troubleshooting systems planned for full implementation in PCI Express 3.0. However, the speed is the same as PCI Express 2.0. The increase in power from the slot breaks backward compatibility between PCI Express 2.1 cards and some older motherboards with 1.0/1.0a, …

HP Z4 G4 Workstation Specifications HP® Customer Support

PCI express hotplug implementation for ATCA based

REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and add-in card specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 2.2 Incorporated ECNs and improved readability 12/18/98 2.3 Incorporated ECNs, errata, and deleted 5 volt only keyed add-in cards 3/29/02 The PCI Special Interest Group disclaims all warranties and liability

The MPEX4S952 4-Port RS232 Mini PCI Express Serial Card (16650 UART) turns a mini-PCIe slot into four RS232 (DB9) serial ports with data rates up to 921.6 Kbps – a cost-saving solution for adding serial support to embedded systems missing the functionality.

Embedded PCIe Graphics REV 1.0 Page 5 of 14 2017 Up to 16k × 16k textures, including 128-bit/pixel texture are supported.

standard configuration mechanisms, registers, and features in Chapter 7 of the PCI Express Base Specification, Revision 1.0a. This specification does not describe the full set of PCI Express tests and assertions for these

Option PCE3 and Option PCE4 provide the complete set of PCI Express 3.0 and 4.0 Base Spec jitter measurements enabling silicon designers to verify that their silicon meets the base specification …

Express Base Specification Revision 3. 0, November 10, 2010.PCI Express Base 2. 0 Specification 4MB – This version includes the change bar. Format specifications are maintained and developed by the PCI-SIG PCI Special.

BASE specification: defines device behavior at the chip level History A new version of each of these specifications is developed for each generation of PCIE 2005: PCIe 1.0, 2.5 Gb/s 2007: PCIe 2.0, 5 Gb/s 2010: PCIe 3.0, 8 Gb/s 2018: PCIe 4.0, 16 Gb/s. The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to

PCIe Base Specification revision 3.0 was made available in Nov 2010. PCIe 3.0 having transfer rate of 8GT/s . PCIe 3.0 Specification include a number of optimizations for enhanced signalling and data integrity, including transmitter and receiver equalization , PLL improvement, clock data recovery and channel enhancements.

The€Smart€Timing€Choice™ 5 SiTAN10026€Rev€1.0 SiT9102JitterPerformance€for PCIExpress€Applications 4 References [1]€ PCISIG,€“PCIExpress€Base€Specification€Revision€1.1”

operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

Interface PCI Express® Base Specification Revision 3.1 (PCIe®) Maximum Speed 32 GT/s (PCIe ® Gen3×4 Lane) Command NVM Express TM Revision 1.2.1 (NVMe TM )

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

Configuration Space Test Considerations Revision 1

PCIe* 4.0 Retimer Supplemental Features and Standard Intel

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

The standards body is just “days away” from releasing version 0.7 of the PCIe Express 4.0 specification to members, according to Solomon. The final specification …

The PCI Express electrical performance validation and compliance software performs a wide range of electrical tests as per the PCI Express 1.0a, 1.1*, for new silicon, add-in cards, and motherboard systems as documented in chapter 4 of the base specification and chapter 4 of the Card Electromechanical specification. In addition to full swing (800 mV) testing, the software also …

I obtained a copy of the latest PCIe 3.0 spec, and section 1.2 titled “PCI Express Link” still states that PCIe is dual-simplex, not full-duplex: “A Link represented a dual-simplex communications channel between two components.” (PCI Express Base Specification, Revision 3.0; Nov. 10, 2010).

The MPEX4S952 4-Port RS232 Mini PCI Express Serial Card (16650 UART) turns a mini-PCIe slot into four RS232 (DB9) serial ports with data rates up to 921.6 Kbps – a cost-saving solution for adding serial support to embedded systems missing the functionality.

PHY Interface for PCI Express, SATA, USB 3.1, DisplayPort, and Converged IO Architectures, this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights (including without limitation rights under any party’s patents) are granted herein. All product names are trademarks, registered trademarks, or service marks of their respective owners

The XIO2001 is a single-function PCI Express to PCI translation bridge that is fully compliant to the PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0. For downstream traffic, the bridge simultaneously supports up to eight posted and four non-posted transactions. For upstream traffic, up to six posted and four non-posted transactions are simultaneously supported. The PCI Express

PCI Express 3.0 Base specification revision 3.0 was made available in November 2010, after multiple delays. In August 2007, PCI-SIG announced that PCI Express 3.0 would carry a bit rate of 8 gigatransfers per second, and that it would be backwards compatible with existing PCIe implementions.

Specifications _ PCI-SIG – Download as PDF File (.pdf), Text File (.txt) or read online. Specifications _ PCI-SIG

Specifications _ PCI-SIG Computer Networking Electronics

4 Port RS232 Mini PCI Express Serial Card w/ 16650 UART

The standards body is just “days away” from releasing version 0.7 of the PCIe Express 4.0 specification to members, according to Solomon. The final specification …

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

PCI-Express Gen-4: o Base Specification revision 4.0 expected to reach version 1.0 in 2017 o Maximum speed: 16 Gbps / Lane / direction o Single- or multi-lane links to …

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

The 2-Port USB 3.0 PCI Express Adapter, model TU3-H2PIE, adds two super speed 5Gbps USB 3.0 ports to a tower computer. Transfer content from USB 3.0 storage enclosures, flash drives, and camcorders at 5Gbps speeds—10 times faster than USB 2.0.

Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s PCIe 4.0 revision 0.5 is expected in Q1 of 2014 while revision 0.9 is expected in Q1 of

The MPEX4S952 4-Port RS232 Mini PCI Express Serial Card (16650 UART) turns a mini-PCIe slot into four RS232 (DB9) serial ports with data rates up to 921.6 Kbps – a cost-saving solution for adding serial support to embedded systems missing the functionality.

operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

• PCI Express Base Specification, Revision 4.0, Version 1.0, October 5, 2017 • System Management Bus (SMBus) Specification , Version 2.0, August 3, 2000 • JTAG Specification (IEEE* 1149.1)

The PCI Express electrical performance validation and compliance software performs a wide range of electrical tests as per the PCI Express 1.0a, 1.1*, for new silicon, add-in cards, and motherboard systems as documented in chapter 4 of the base specification and chapter 4 of the Card Electromechanical specification. In addition to full swing (800 mV) testing, the software also …

4.0 Version 0.3: Based on PCI Express® Base Specification Revision 3.1 (November 7, 2013) with some editorial feedback received in December 2013. • Added Chapter 9, Electrical Sub-block: Separated Section 4.3 of the 3.1 Base

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports

BASE specification: defines device behavior at the chip level History A new version of each of these specifications is developed for each generation of PCIE 2005: PCIe 1.0, 2.5 Gb/s 2007: PCIe 2.0, 5 Gb/s 2010: PCIe 3.0, 8 Gb/s 2018: PCIe 4.0, 16 Gb/s. The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to

4 Port RS232 Mini PCI Express Serial Card w/ 16650 UART

SYBA 4-Port USB 3.0 PCI-Express Card x1 Revision 1.0

standard configuration mechanisms, registers, and features in Chapter 7 of the PCI Express Base Specification, Revision 1.0a. This specification does not describe the full set of PCI Express tests and assertions for these

The processor supports up to 4 channels of DDR4 memory. To realize full performance at least one DIMM must be inserted into each channel. The CPUs determine the speed at …

The PCI Express Base Specification, Revision 4.0, Version 0.7, is quite complex, exceeding 1,000 pages, making it challenging for test engineers to quickly come up to speed. Tektronix works closely with industry organizations such as PCI-SIG to help translate industry specification test requirements into easy-to-use turnkey test solutions that offer clear and concise characterization reports

I obtained a copy of the latest PCIe 3.0 spec, and section 1.2 titled “PCI Express Link” still states that PCIe is dual-simplex, not full-duplex: “A Link represented a dual-simplex communications channel between two components.” (PCI Express Base Specification, Revision 3.0; Nov. 10, 2010).

Addendum to the PCI Express Base Specification Revision 1.0. Find us at www.keysight.com Page 3 Features The Keysight N5393F/G PCI Express 4.0 electrical transmitter (TX) test software represents the . latest PCI Express TX test tool that supports PCI Express 4.0 with speeds of up 16 GT/s. Below is a list of a few of the key features of this software package. – PCIe 4.0 BASE TX measurements

PCI Express devices communicate via a logical connection called an interconnect or link. A link is a point-to-point communication channel between two PCI Express ports allowing both of them to send and receive ordinary PCI requests (configuration, I/O or memory read/write) and interrupts (INTx, MSI or …

The MPEX4S952 4-Port RS232 Mini PCI Express Serial Card (16650 UART) turns a mini-PCIe slot into four RS232 (DB9) serial ports with data rates up to 921.6 Kbps – a cost-saving solution for adding serial support to embedded systems missing the functionality.

Express Base Specification Revision 3. 0, November 10, 2010.PCI Express Base 2. 0 Specification 4MB – This version includes the change bar. Format specifications are maintained and developed by the PCI-SIG PCI Special.

QPHY-PCIe3 Teledyne LeCroy QPHY-PCIe3 Test Solution provides automated control for Teledyne LeCroy oscilloscopes for performing transmitter physical layer tests as described by the PCI Express Base Specification Revision 3.0 Version 0.9 and the Card Electromechanical Specification Revision 3.0 Version 0.7.

operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

• PCI Express Base Specification, Revision 4.0, Version 1.0, October 5, 2017 • System Management Bus (SMBus) Specification , Version 2.0, August 3, 2000 • JTAG Specification (IEEE* 1149.1)

The€Smart€Timing€Choice™ 5 SiTAN10026€Rev€1.0 SiT9102JitterPerformance€for PCIExpress€Applications 4 References [1]€ PCISIG,€“PCIExpress€Base€Specification€Revision€1.1”

The core is fully compliant with the current version of the PCI Express Base Specification 4.0. The core includes all of the required 4.0 features including Physical functions, SR-IOV, flexible equalization support. The core has been extensively validated with the Avery Logic PCI-Xactor PCI Express Compliance Suite and Northwest Logic Expresso Testbench. Northwest Logic also provides IP Core

PCI Express explained Everything Explained Today

Specifications _ PCI-SIG Computer Networking Electronics

REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and add-in card specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 2.2 Incorporated ECNs and improved readability 12/18/98 2.3 Incorporated ECNs, errata, and deleted 5 volt only keyed add-in cards 3/29/02 The PCI Special Interest Group disclaims all warranties and liability

The€Smart€Timing€Choice™ 5 SiTAN10026€Rev€1.0 SiT9102JitterPerformance€for PCIExpress€Applications 4 References [1]€ PCISIG,€“PCIExpress€Base€Specification€Revision€1.1”

The PCI-SIG ®, the organization responsible for the PCI Express ® (PCIe ®) standard, released the PCI Express Base Specification Revision 4.0 Version 1.0 in 2017. This specification doubles the throughput of PCIe from approximately 1GBs per lane to approximately 2GBs per lane.

revision 1.1 to 2.0 to 2.1 to 3.0 to 3.1 and finally to 4.0. There is a very large number of features and There is a very large number of features and optional behavior for PCIe.

PCIe 4.0 will essentially double the interconnect performance bandwidth of the current 3.0 specification, from 8 gigatransfers per second (GTps) to 16GTps.

the PCI Express Base Specification Revision 2.0 and the PCI Express Card Electromechanical The GTX transceiver is configured using version 1.5 of the Table 3: Revision 2.0 PCI Express Specification Characterization Summary of Results Test Parameter Specification Worst-Case Test Result Units Compliant Transmitter Unit Interval Min 199.94 200.01 ps Yes Max 200.06 200.01 ps …

1. Introduction. Peripheral Component Interconnect Express (PCIe) hotplug is derived from revision 1.0 of the standard hotplug controller specification for PCI . This specification describes the methodology by which PCIe endpoint devices may be added/removed from an operational system without compromising the operational state of the system.

The€Smart€Timing€Choice™ 5 SiTAN10026€Rev€1.0 SiT9102JitterPerformance€for PCIExpress€Applications 4 References [1]€ PCISIG,€“PCIExpress€Base€Specification€Revision€1.1”

PCI Express® Transmitter Compliance/Debug Solution DPO

PCI Express explained Everything Explained Today

PCI Express 4.0 (PCIe Gen4) Microsemi

PHY Interface for PCI Express, SATA, USB 3.1, DisplayPort, and Converged IO Architectures, this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights (including without limitation rights under any party’s patents) are granted herein. All product names are trademarks, registered trademarks, or service marks of their respective owners

PCI Express 4 teledynelecroy.com.cn

PCI express hotplug implementation for ATCA based

AN 829 PCI Express* Avalon®-MM DMA Reference Design

Embedded PCIe Graphics REV 1.0 Page 5 of 14 2017 Up to 16k × 16k textures, including 128-bit/pixel texture are supported.

Specifications _ PCI-SIG Computer Networking Electronics

Mini PCIe Serial Card PCI Express RS232 – StarTech.com

Express Base Specification Revision 3. 0, November 10, 2010.PCI Express Base 2. 0 Specification 4MB – This version includes the change bar. Format specifications are maintained and developed by the PCI-SIG PCI Special.

HP Z4 G4 Workstation Specifications HP® Customer Support

PCI Express 4.0 (PCIe Gen4) Microsemi

PCI-Express Gen-4: o Base Specification revision 4.0 expected to reach version 1.0 in 2017 o Maximum speed: 16 Gbps / Lane / direction o Single- or multi-lane links to …

PCI Express 4.0 Course Outline MindShare

operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

Configuration Space Test Considerations Revision 1

Earlier this week PCI-SIG revealed the specifications for PCI Express 3.1 and 4.0 according to Tom’s PCIe 4.0 revision 0.5 is expected in Q1 of 2014 while revision 0.9 is expected in Q1 of

PCI express hotplug implementation for ATCA based

PCI Express 4.0 Course Outline MindShare

This specification is a companion for the PCI Expres… view more This specification is a companion for the PCI Express Base Specification, Revision 1.1. Its primary focus is the implementation of an evolutionary strategy with the current PCI desktop/server mechanical and electrical specifications. The discussions are confined to ATX or ATX-based form factors. Other form factors, such as PCI

AN 829 PCI Express* Avalon®-MM DMA Reference Design

N5393G PCI Express® Electrical Performance Keysight

PCI Express explained Everything Explained Today

4.0 Version 0.3: Based on PCI Express® Base Specification Revision 3.1 (November 7, 2013) with some editorial feedback received in December 2013. • Added Chapter 9, Electrical Sub-block: Separated Section 4.3 of the 3.1 Base

PCIe 4.0 to hit 16 GT/s base spec due in 2014-2015 The

1. Introduction. Peripheral Component Interconnect Express (PCIe) hotplug is derived from revision 1.0 of the standard hotplug controller specification for PCI . This specification describes the methodology by which PCIe endpoint devices may be added/removed from an operational system without compromising the operational state of the system.

AN 829 PCI Express* Avalon®-MM DMA Reference Design

SYBA 4-Port USB 3.0 PCI-Express Card x1 Revision 1.0

PCIe* 4.0 Retimer Supplemental Features and Standard Intel

The PCI-SIG ®, the organization responsible for the PCI Express ® (PCIe ®) standard, released the PCI Express Base Specification Revision 4.0 Version 1.0 in 2017. This specification doubles the throughput of PCIe from approximately 1GBs per lane to approximately 2GBs per lane.

N5393G PCI Express® Electrical Performance Keysight

Configuration Space Test Considerations Revision 1

PCI-SIG ENGINEERING CHANGE NOTICE

operate in compliance with the existing PCI Express 1.1 Base Specification. The services for Switches to provide enhanced access control for ATS functionality are fully defined in this ACS ECN.

HP Z4 G4 Workstation Specifications HP® Customer Support

Topic End-to-End System-Level Simulations Xilinx

PCIe Base Specification revision 3.0 was made available in Nov 2010. PCIe 3.0 having transfer rate of 8GT/s . PCIe 3.0 Specification include a number of optimizations for enhanced signalling and data integrity, including transmitter and receiver equalization , PLL improvement, clock data recovery and channel enhancements.

Embedded PCIe Graphics Advantech

PCI Express® Transmitter Compliance/Debug Solution DPO