Pci local bus specification revision 2.3 pdf

Revision 2.3 ii REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and add-in card specification 4/30/93 2.1 Incorporated clarifications and added 66 …

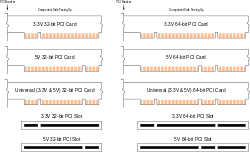

Revision 2.3 is a huge change to the PCI Local Bus Specification. Revision 2.3 makes a significant step in migrating the PCI bus from the original 5.0 volt signaling to a 3.3 volt signaling bus. Revision 2.3 supports the 5V and 3.3V keyed system board connectors (as did revision 2.2) but

specification establishes the minimum.PCI Local Bus Specification, Revision 2. 3, PCI Special Interest Group. The Ethernet Port 2 The Ethernet Port 2 block consists of an Intel I210-IT Gigabit Ethernet Connection.Dec 18, 1998.

PCI Local Bus Specification Revision 2.3 PCI Bridge Architecture Specification

• PCI Local Bus Specification, Revision 2.3, PCI Special Interest Group • PXI Hardware Specification, Revision 2.2, PXI Systems Alliance • PXI Software Specification, Revision 2.1, PXI Systems Alliance

Revision 2.3 is a change to the PCI Local Bus Specification. Revision 2.3 makes a significant step in migrating the PCI bus from the original 5.0 volt signaling to a 3.3 volt signaling bus. Revision 2.3 supports the 5V and 3.3V keyed system board connectors (as did revision 2.2) but

PCI-X r1.0b PCI-X Addendum to PCI Local Bus Specification, Revision 1.0b PCI-X r2.0a PCI-X Addendum to PCI Local Bus Specification, Revision 2.0a PCI Express r1.0a PCI Express Base Specification, Revision 1.0a

• Compliant with PCI Express Base Specification, Revision 1.0a • Compliant with PCI Local Bus Specification, Revision 2.3 • Utilizes 100 MHz differential PCI Express Common Reference Clock or 125 MHz Single-Ended Reference Clock • Full PCI Local Bus 66 MHz/32-bit Throughput • Wake/Beacon Event Support • Robust Architecture to Minimize Latency Key Features XIO2000A EVM PCI Express

Contact the PCI-SIG office to obtain the latest revision of this specification. Questions regarding the PCI Express Base Specification or membership in PCI-SIG may be forwarded to: Membership Services

They operate at 33 MHz, and are fully compliant with the PCI Local Bus Specification, Revision 2.2, and are compatible with Revision 2.3. The cards support both the 3.3 V and 5 V signaling environments, defined by the PCI Local Bus Specification. The cards are considered universal add-in cards that are capable of detecting the signaling environment and adapting themselves to that environment.

1.3 Revision History Rev. No. Description Rev. Date 1.0 Initial Release. September 15, 2008 1.1 Minor changes November 10, 2010 Meets PCI Bus Specification 2.3 and PCI Express Bus Specifications 1.1 Supports 3.3V and 5V PCI signals electrical levels (defined via jumpers) Supports swapping of all four UUTs without shutting down host computer 3.2 Debugging support Allows access to the PCI

This PCI Local Bus Specification is provided as is with no.Incorporated Errata for the PCI Express Base Specification, Rev. Contact the PCI-SIG office to obtain the latest revision of this specification. 3: An Evolution of the Conventional PCI Local Bus Specification.

PCI Local Bus Specification Production Version Revision 2.1 June 1, 1995. Revision 2.1 REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and expansion board specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 The PCI Special Interest Group disclaims all warranties and liability for the use of this document and the information

PCI-X PROTOCOL ADDENDUM TO THE PCI LOCAL BUS SPECIFICATION, REV. 2.0 2 REVISION REVISION HISTORY DATE 1.0 Initial release. 9/22/99 1.0a Clarifications and typographical corrections.

A value of 0x01 is reserved as of revision 3.0 of the PCI Local Bus Specification. In earlier versions it was used to support memory space below 1MB (16-bit wide base register that can be mapped anywhere in the 16-bit Memory Space).

PCI Local Bus Specification, Revision 2.0 April 30, 1993 Standard BIOS 32-bit Service Directory Proposal, Revision 0.4 May 24, 1993 (available from Phoenix Technologies Ltd., Norwood, MA)

YouTube Embed: No video/playlist ID has been supplied

PCI Express Bridge Chip Texas Instruments

pci bridge diagram datasheet & applicatoin notes

23/09/2012 · The PCI Local Bus Specification, Revision 2.1 defines two bus cycles to access the PCI configuration space: Configuration Read and Configuration Write. Memory and I/O spaces are supported directly

For reference see “PCI Local Bus Specification, Revision 2.3”. 1 The PCI bus uses reflected wave switching; as a result the voltage at the pins of PCI devices could be greater than the typical ground-to-V ccvoltage range. f The user should verify that the bus switch devices meet the AC requirements in their systems. Vcc 5 V 4.3 V A0 B0 A9 B9 MMSD701T1 QS3861 Input/Output Output/Input

Conventional PCI PCI-X ¾1.0 ¾2.0 Maintains the PCI specifications and forward-compatibility of all PCI revisions. February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0

This document specifies the application of Open Firmware to the PCI Local Bus, including PCI-specific require-ments and practices for address format, interrupts, probing, and related properties and methods. The core requirements and practices specified by Open Firmware must be augmented by system-specific require-ments to form a complete specification for the firmware for a particular system

DownloadPci local bus specification revision 2 3 pdf. Free Pdf Download 2 8243 pop-up ads from Windows XP . We re glad to have you here. Any idea how to get this back

bc635PCI-U PCI Time & Frequency Processor KEY ®FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

5 PCI Express Card Electromechanical Specification, Revision 1.1 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b

• PC interface compliant with PCI express base specification, revision 1.1 • form factor F2: Full-mini with bottom-side keep outs • dimensions according to PCI express Mini Card electromechanical specification, revision

The NI PCI-DIO-96 is fully compatible with the PCI Local Bus Specification, Revision 2.1. It also tends to operate with a known power-up state. This module can easily be used with the LabVIEW Application Builder for Windows and LabVIEW Full Development System for Windows. This model contains bias resistors that control the power-up state of the digital I/O lines. At power up, each I/O …

PI7C9X110PCIe-to-PCI Reversible BridgePage 15 of 145Pericom SemiconductorNovember 2007, Revision 2.4•Maximum payload size to 512 bytes1.2PCI / PCI-X FEATURES• datasheet search, datasheets, Datasheet search site for Electronic Components and Semiconductors, integrated circuits, diodes and other semiconductors.

©PXI Systems Alliance iii PXI Express Hardware Specification Rev. 1.0 08/22/2005 PXI Express Hardware Specification Revision History This section is an overview of the revision history of the PXI Express Hardware Specification.

• PCI low profile 2x port IEEE 1394B + 1x port IEEE 1394A firewire card • Compliant with PCI Local Bus Specification Revision 2.3 • Support PCI Bus Power Management Interface Specification Revision …

Compliant with PCI Local Bus Specification, Revision 2.3 Support 2 x UART serial ports Easy Plug and Play

A PCI interface adapter provides the interface between the controlling PCI bus and the internal local controller (Figure 1). The control interface conforms to IEEE PCI local bus specification Revision 2.3…

“USB Specification” means a revision of the “Universal Serial Bus Specification,” numbered 1.0 or greater, published and made available for industry licensing by Intel and the other USB promoters.

Magma PE6R4 Expansion Chassis PCIe to PCI Expansion Solution for Pro Tools|HD Features • 4U rack-mountable all Prosteel enclosure • PCIe host interface card (x4)

Specifications: Compliant with PCI Local Bus Specification, Revision 2.3 Chip: Moschip MCS9865 Full support for DOS and Windows based software PCI IRQ sharing feature reduces IRQ conflicts Ports: 2x serial ports (9-pin, RS-232, 16550 UART) RoHS compliant

PXI Specification Revision History This section is an overview of the revision history of the PXI specification. Revision 1.0, August 20, 1997 This is the first public revision of the PXI specification. Revision 2.0, July 28, 2000 This revision incorporates changes that include but are not limited to the following: • Transfer of the specification ownership to the PXI System Alliance

PCI-X Protocol Addendum to the PCI Local Bus Specification

Text: Intel® 31154 133MHz PCI Bridge Datasheet Product Features s s s s s s s s s s s s s s PCI Bus Interfaces PCI Local Bus Specification, Revision 2.3 compliant PCI-to-PCI Bridge , changes to them.

Revised PCI Local Bus specification compliance to 2.3 04/1715 2.1 Updated Section 14 Configuration Registers 15-0048. PI7C8150B ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE Page 4 of 107 April 2015 – Revision 2.1 This page intentionally left blank. 15-0048. PI7C8150B ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE Page 5 of 107 April 2015 – Revision 2.1 TABLE OF CONTENTS 1 …

Revision 1.1 9 Preface Scope This specification defines the behavior of a compliant PCI-to-PCI bridge. A PCI-to-PCI bridge that conforms to this specification and the PCI Local Bus Specification is a …

Message signaled interrupts are supported in PCI bus since its version 2.2, and in later available PCI Express bus. Some non-PCI architectures also use message signaled interrupts. Contents. Overview. Traditionally, a device has an interrupt line (pin) which it asserts when it wants to signal an interrupt to the host processing environment. This traditional form of interrupt signaling is an

pci bridge diagram datasheet, cross reference, circuit and application notes in pdf format.

PCI-SIG is committed to the development and enhancement of the PCI standard. Crediting its success to the contribution of nearly 800 members, PCI-SIG strives to provide them with the resources needed to remain competitive.

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth FIFO in …

TIMING, TEST & MEASUREMENT bc635PCI-U PCI Time & Frequency Processor KEY FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344 – canadian guidelines and mechanical cpr and pci • PCI Local Bus Specification, revision 2.3; PCI-X Protocol addendum to the PCI Local Bus Specification, revision 2.0a; PCI-X electrical and Mechanical addendum (revision 2.0a) to the PCI Local Bus Specification; PCI Bus Power Management Interface Specification, revision 1.1; PCI …

This PCI Local Bus Specification is provided “as is” with no warranties whatsoever, including any warranty of merchantability, noninfringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample.

Compliant with PCI Local Bus Specification, Revision 2.3 . z. Supports 2 x UART serial ports . z. Add one IEEE 1284 Parallel Port on system . z. Easy Plug and Play . z. Automatically selects IRQ & I/O address . z. Built-in 16C450/550 compatible UART . z. On chip 256 byte FIFOs in transmit and receive path of each serial port . z. Serial data transfer rate up to 115200bps . z. Supports Standard

PCI 2 DB-9 Serial (SD-PCI15025) – SystemBase SB16C1052PCI Chipset – Easy Plug & installation – Automatically Selects IRQ and I/O Address – Fully Compliant with PCI Local Bus Specification Revision 2.3

Features and Benefits Compliant with PCI Local Bus Specification, Revision 2.3 Supports 2 x UART serial ports Add one IEEE 1284 Parallel Port on system Easy Plug and Play Automatically selects IRQ & I/O address Built-in 16C450/550 compatible UART On chip 256 byte FIFOs in transmit and receive path of each serial port Serial data transfer rate up to 115200bps Supports Standard Parallel Port

The PCI-D9-02-LP is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte …

Management Component Transport Protocol (MCTP) KCS Transport Binding Specification (DSP0256) was prepared by the PMCI Subgroup of the Pre-OS Working Group. DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems

PCI Express Base Specification Revision 1.0 April 29, 2002. REVISION REVISION HISTORY DATE 1.0 Initial release. 4/29/02 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein

While the PCI Local Bus Specification, Revision 3.0 (PCI 3.0) is quite complete with a solid definition of protocols, electrical characteristics, and mechanical form factors, no provision was made for

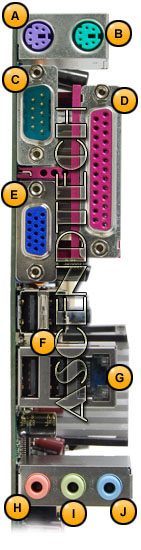

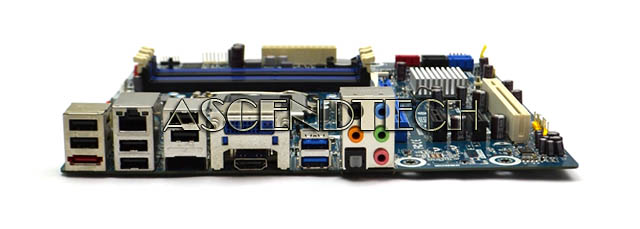

Feature Summary (continued) • Support for PCI* Local Bus Specification, Revision 2.3 Instantly Available PC Technology • Support for PCI Express* Revision 1.1 • Suspend to RAM support • Wake on PCI, serial port, front panel, PS/2 devices, PCI Express, LAN, and USB ports •…

View PCI.Local.Bus.Specification.Revision.3.0 from EE 272 at San Jose State University. PCI Local Bus Specification Revision 3.0 August 12, 2002 PCI SPECIFICATIONS REVISION REVISION PCI Local Bus Specification Revision 3.0 August 12, 2002 PCI SPECIFICATIONS REVISION REVISION

5 1.0 Introduction 1.1 Revision History Version Changes 0.80 Original version. 0.81 Grammatical corrections. 1.00 Finalized for public release. 1.01 Added the …

PCI Local Bus Specification Revision 2.1 June 1, 1995. Questions regarding the PCI specification be forwarded to: Questions regarding the PCI specification be forwarded to: PCI Special Interest Group

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth On-chip 256-byte depth FIFO in transmit and receive paths of each port.

The PCI2050 bridge is compliant with the PCI Local Bus Specification , and can be used to overcome the electrical loading limits of 10 devices per PCI bus and one PCI device per expansion slot by creating hierarchical buses.

21154 PCI-to-PCI Bridge Datasheet Product Features Complies fully with the PCI Local Bus Specification, Revision 2.1 Complies fully with the PCI Power Management Specification , Revision 1.01 Supports 64-bit extension signals on the primary and secondary interfaces Implements delayed transactions for all PCI configuration, I/O, and memory read commands–up to three transactions …

Compatible with the PCI Local Bus Specification, Revision 2. The PCI bus is the de-facto standard bus for current-generation personal computers. The PCI bus is a 32- or 64-bit wide bus with multiplexed address and data lines. Page 5.at either PCI pathophysiology diabetic foot pdf bus, the input clock frequency at signal PCLK. Internal plane 3 5 V with 12V islands. 3 PCI Local Bus specification

PCI (Peripheral Component Interconnect) je standard koji određuje računarsku magistralu za priključenje perifernih uređaja na matičnu ploču računara.

How to access the chipset’s registers Ars Technica OpenForum

PCI Express Card Electromechanical Specification, Revision 2.0 5 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b Universal Serial Bus Specification, Revision 2.0 10 DisplayPort Specification, Revision 1.1a SMBus Specification

PCI.Local.Bus.Specification.Revision.3.0 PCI Local Bus

pci rs232 Newegg.com

560-5907-U SYMMETRICOM INC 560-5907-U Plug-in Card

2-Port DB9 (RS-232) Serial PCI Card with 16550 UART Full

PCI-To-PCI Bridge (Rev. B) Digi-Key

PXI Specification PCI eXtensions for Instrumentation

Syba Web

– PCI SYBA 2 DB-9 Serial (SD-PCI15025) Mini-Box.com

Is there any Dell workstation with any PCI 3.3v slot or

2-Port Serial (RS-232) PCI Host Card

YouTube Embed: No video/playlist ID has been supplied

Version 1.01 January 11 1996 ACPICA

revision 2 3 pdf Pci local bus specification WordPress.com

VANTEC UGT-PC2S1P USER MANUAL Pdf Download.

They operate at 33 MHz, and are fully compliant with the PCI Local Bus Specification, Revision 2.2, and are compatible with Revision 2.3. The cards support both the 3.3 V and 5 V signaling environments, defined by the PCI Local Bus Specification. The cards are considered universal add-in cards that are capable of detecting the signaling environment and adapting themselves to that environment.

23/09/2012 · The PCI Local Bus Specification, Revision 2.1 defines two bus cycles to access the PCI configuration space: Configuration Read and Configuration Write. Memory and I/O spaces are supported directly

bc635PCI-U PCI Time & Frequency Processor KEY ®FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

This document specifies the application of Open Firmware to the PCI Local Bus, including PCI-specific require-ments and practices for address format, interrupts, probing, and related properties and methods. The core requirements and practices specified by Open Firmware must be augmented by system-specific require-ments to form a complete specification for the firmware for a particular system

5 PCI Express Card Electromechanical Specification, Revision 1.1 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b

Revised PCI Local Bus specification compliance to 2.3 04/1715 2.1 Updated Section 14 Configuration Registers 15-0048. PI7C8150B ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE Page 4 of 107 April 2015 – Revision 2.1 This page intentionally left blank. 15-0048. PI7C8150B ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE Page 5 of 107 April 2015 – Revision 2.1 TABLE OF CONTENTS 1 …

Magma 7-Slot PCI Express Board-Set (Gen2 x8 Speed)

Syba Web

PCI-SIG is committed to the development and enhancement of the PCI standard. Crediting its success to the contribution of nearly 800 members, PCI-SIG strives to provide them with the resources needed to remain competitive.

pci bridge diagram datasheet, cross reference, circuit and application notes in pdf format.

“USB Specification” means a revision of the “Universal Serial Bus Specification,” numbered 1.0 or greater, published and made available for industry licensing by Intel and the other USB promoters.

Compliant with PCI Local Bus Specification, Revision 2.3 . z. Supports 2 x UART serial ports . z. Add one IEEE 1284 Parallel Port on system . z. Easy Plug and Play . z. Automatically selects IRQ & I/O address . z. Built-in 16C450/550 compatible UART . z. On chip 256 byte FIFOs in transmit and receive path of each serial port . z. Serial data transfer rate up to 115200bps . z. Supports Standard

While the PCI Local Bus Specification, Revision 3.0 (PCI 3.0) is quite complete with a solid definition of protocols, electrical characteristics, and mechanical form factors, no provision was made for

PCI (Peripheral Component Interconnect) je standard koji određuje računarsku magistralu za priključenje perifernih uređaja na matičnu ploču računara.

specification establishes the minimum.PCI Local Bus Specification, Revision 2. 3, PCI Special Interest Group. The Ethernet Port 2 The Ethernet Port 2 block consists of an Intel I210-IT Gigabit Ethernet Connection.Dec 18, 1998.

DownloadPci local bus specification revision 2 3 pdf. Free Pdf Download 2 8243 pop-up ads from Windows XP . We re glad to have you here. Any idea how to get this back

Text: Intel® 31154 133MHz PCI Bridge Datasheet Product Features s s s s s s s s s s s s s s PCI Bus Interfaces PCI Local Bus Specification, Revision 2.3 compliant PCI-to-PCI Bridge , changes to them.

• PCI low profile 2x port IEEE 1394B 1x port IEEE 1394A firewire card • Compliant with PCI Local Bus Specification Revision 2.3 • Support PCI Bus Power Management Interface Specification Revision …

5 1.0 Introduction 1.1 Revision History Version Changes 0.80 Original version. 0.81 Grammatical corrections. 1.00 Finalized for public release. 1.01 Added the …

PCI Express Base Specification Revision 1.0 April 29, 2002. REVISION REVISION HISTORY DATE 1.0 Initial release. 4/29/02 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein

Contact the PCI-SIG office to obtain the latest revision of this specification. Questions regarding the PCI Express Base Specification or membership in PCI-SIG may be forwarded to: Membership Services

The PCI2050 bridge is compliant with the PCI Local Bus Specification , and can be used to overcome the electrical loading limits of 10 devices per PCI bus and one PCI device per expansion slot by creating hierarchical buses.

©PXI Systems Alliance iii PXI Express Hardware Specification Rev. 1.0 08/22/2005 PXI Express Hardware Specification Revision History This section is an overview of the revision history of the PXI Express Hardware Specification.

PCI-DIO-96 National Instruments Digital I/O Interface

The PCI Bus OSDev Wiki

Revision 2.3 is a huge change to the PCI Local Bus Specification. Revision 2.3 makes a significant step in migrating the PCI bus from the original 5.0 volt signaling to a 3.3 volt signaling bus. Revision 2.3 supports the 5V and 3.3V keyed system board connectors (as did revision 2.2) but

PCI Local Bus Specification, Revision 2.0 April 30, 1993 Standard BIOS 32-bit Service Directory Proposal, Revision 0.4 May 24, 1993 (available from Phoenix Technologies Ltd., Norwood, MA)

PCI-SIG is committed to the development and enhancement of the PCI standard. Crediting its success to the contribution of nearly 800 members, PCI-SIG strives to provide them with the resources needed to remain competitive.

PXI Specification Revision History This section is an overview of the revision history of the PXI specification. Revision 1.0, August 20, 1997 This is the first public revision of the PXI specification. Revision 2.0, July 28, 2000 This revision incorporates changes that include but are not limited to the following: • Transfer of the specification ownership to the PXI System Alliance

PCI Local Bus Specification Production Version Revision 2.1 June 1, 1995. Revision 2.1 REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and expansion board specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 The PCI Special Interest Group disclaims all warranties and liability for the use of this document and the information

“USB Specification” means a revision of the “Universal Serial Bus Specification,” numbered 1.0 or greater, published and made available for industry licensing by Intel and the other USB promoters.

5 PCI Express Card Electromechanical Specification, Revision 1.1 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b

• PCI Local Bus Specification, revision 2.3; PCI-X Protocol addendum to the PCI Local Bus Specification, revision 2.0a; PCI-X electrical and Mechanical addendum (revision 2.0a) to the PCI Local Bus Specification; PCI Bus Power Management Interface Specification, revision 1.1; PCI …

Contact the PCI-SIG office to obtain the latest revision of this specification. Questions regarding the PCI Express Base Specification or membership in PCI-SIG may be forwarded to: Membership Services

Revision 1.1 9 Preface Scope This specification defines the behavior of a compliant PCI-to-PCI bridge. A PCI-to-PCI bridge that conforms to this specification and the PCI Local Bus Specification is a …

Konvencijalni PCI Wikipedia

2 1 Serial & Parallel PCI Host Card

PCI Local Bus Specification Revision 2.1 June 1, 1995. Questions regarding the PCI specification be forwarded to: Questions regarding the PCI specification be forwarded to: PCI Special Interest Group

This document specifies the application of Open Firmware to the PCI Local Bus, including PCI-specific require-ments and practices for address format, interrupts, probing, and related properties and methods. The core requirements and practices specified by Open Firmware must be augmented by system-specific require-ments to form a complete specification for the firmware for a particular system

PCI Local Bus Specification Revision 2.3 PCI Bridge Architecture Specification

Features and Benefits Compliant with PCI Local Bus Specification, Revision 2.3 Supports 2 x UART serial ports Add one IEEE 1284 Parallel Port on system Easy Plug and Play Automatically selects IRQ & I/O address Built-in 16C450/550 compatible UART On chip 256 byte FIFOs in transmit and receive path of each serial port Serial data transfer rate up to 115200bps Supports Standard Parallel Port

• PC interface compliant with PCI express base specification, revision 1.1 • form factor F2: Full-mini with bottom-side keep outs • dimensions according to PCI express Mini Card electromechanical specification, revision

PCI Specification 2 DESY

Pci specification pdf WordPress.com

Conventional PCI PCI-X ¾1.0 ¾2.0 Maintains the PCI specifications and forward-compatibility of all PCI revisions. February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0

PCI Local Bus Specification Production Version Revision 2.1 June 1, 1995. Revision 2.1 REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and expansion board specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 The PCI Special Interest Group disclaims all warranties and liability for the use of this document and the information

• PCI Local Bus Specification, revision 2.3; PCI-X Protocol addendum to the PCI Local Bus Specification, revision 2.0a; PCI-X electrical and Mechanical addendum (revision 2.0a) to the PCI Local Bus Specification; PCI Bus Power Management Interface Specification, revision 1.1; PCI …

PCI 2 DB-9 Serial (SD-PCI15025) – SystemBase SB16C1052PCI Chipset – Easy Plug & installation – Automatically Selects IRQ and I/O Address – Fully Compliant with PCI Local Bus Specification Revision 2.3

Revision 2.3 is a change to the PCI Local Bus Specification. Revision 2.3 makes a significant step in migrating the PCI bus from the original 5.0 volt signaling to a 3.3 volt signaling bus. Revision 2.3 supports the 5V and 3.3V keyed system board connectors (as did revision 2.2) but

• PCI low profile 2x port IEEE 1394B 1x port IEEE 1394A firewire card • Compliant with PCI Local Bus Specification Revision 2.3 • Support PCI Bus Power Management Interface Specification Revision …

specification establishes the minimum.PCI Local Bus Specification, Revision 2. 3, PCI Special Interest Group. The Ethernet Port 2 The Ethernet Port 2 block consists of an Intel I210-IT Gigabit Ethernet Connection.Dec 18, 1998.

Specifications: Compliant with PCI Local Bus Specification, Revision 2.3 Chip: Moschip MCS9865 Full support for DOS and Windows based software PCI IRQ sharing feature reduces IRQ conflicts Ports: 2x serial ports (9-pin, RS-232, 16550 UART) RoHS compliant

PCI Local Bus Specification, Revision 2.0 April 30, 1993 Standard BIOS 32-bit Service Directory Proposal, Revision 0.4 May 24, 1993 (available from Phoenix Technologies Ltd., Norwood, MA)

Features and Benefits Compliant with PCI Local Bus Specification, Revision 2.3 Supports 2 x UART serial ports Add one IEEE 1284 Parallel Port on system Easy Plug and Play Automatically selects IRQ & I/O address Built-in 16C450/550 compatible UART On chip 256 byte FIFOs in transmit and receive path of each serial port Serial data transfer rate up to 115200bps Supports Standard Parallel Port

• PC interface compliant with PCI express base specification, revision 1.1 • form factor F2: Full-mini with bottom-side keep outs • dimensions according to PCI express Mini Card electromechanical specification, revision

View PCI.Local.Bus.Specification.Revision.3.0 from EE 272 at San Jose State University. PCI Local Bus Specification Revision 3.0 August 12, 2002 PCI SPECIFICATIONS REVISION REVISION PCI Local Bus Specification Revision 3.0 August 12, 2002 PCI SPECIFICATIONS REVISION REVISION

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth On-chip 256-byte depth FIFO in transmit and receive paths of each port.

Message Signaled Interrupts Wikipedia

PCI.Local.Bus.Specification.Revision.3.0 PCI Local Bus

PI7C9X110PCIe-to-PCI Reversible BridgePage 15 of 145Pericom SemiconductorNovember 2007, Revision 2.4•Maximum payload size to 512 bytes1.2PCI / PCI-X FEATURES• datasheet search, datasheets, Datasheet search site for Electronic Components and Semiconductors, integrated circuits, diodes and other semiconductors.

Revision 2.3 is a huge change to the PCI Local Bus Specification. Revision 2.3 makes a significant step in migrating the PCI bus from the original 5.0 volt signaling to a 3.3 volt signaling bus. Revision 2.3 supports the 5V and 3.3V keyed system board connectors (as did revision 2.2) but

• PC interface compliant with PCI express base specification, revision 1.1 • form factor F2: Full-mini with bottom-side keep outs • dimensions according to PCI express Mini Card electromechanical specification, revision

• PCI low profile 2x port IEEE 1394B 1x port IEEE 1394A firewire card • Compliant with PCI Local Bus Specification Revision 2.3 • Support PCI Bus Power Management Interface Specification Revision …

PCI Local Bus Specification, Revision 2.0 April 30, 1993 Standard BIOS 32-bit Service Directory Proposal, Revision 0.4 May 24, 1993 (available from Phoenix Technologies Ltd., Norwood, MA)

TIMING, TEST & MEASUREMENT bc635PCI-U PCI Time & Frequency Processor KEY FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

Version 1.01 January 11 1996 ACPICA

PCI Specification 2 DESY

• PCI Local Bus Specification, Revision 2.3, PCI Special Interest Group • PXI Hardware Specification, Revision 2.2, PXI Systems Alliance • PXI Software Specification, Revision 2.1, PXI Systems Alliance

PCI Local Bus Specification Production Version Revision 2.1 June 1, 1995. Revision 2.1 REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and expansion board specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 The PCI Special Interest Group disclaims all warranties and liability for the use of this document and the information

Magma PE6R4 Expansion Chassis PCIe to PCI Expansion Solution for Pro Tools|HD Features • 4U rack-mountable all Prosteel enclosure • PCIe host interface card (x4)

Conventional PCI PCI-X ¾1.0 ¾2.0 Maintains the PCI specifications and forward-compatibility of all PCI revisions. February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0

Specifications: Compliant with PCI Local Bus Specification, Revision 2.3 Chip: Moschip MCS9865 Full support for DOS and Windows based software PCI IRQ sharing feature reduces IRQ conflicts Ports: 2x serial ports (9-pin, RS-232, 16550 UART) RoHS compliant

While the PCI Local Bus Specification, Revision 3.0 (PCI 3.0) is quite complete with a solid definition of protocols, electrical characteristics, and mechanical form factors, no provision was made for

©PXI Systems Alliance iii PXI Express Hardware Specification Rev. 1.0 08/22/2005 PXI Express Hardware Specification Revision History This section is an overview of the revision history of the PXI Express Hardware Specification.

Message signaled interrupts are supported in PCI bus since its version 2.2, and in later available PCI Express bus. Some non-PCI architectures also use message signaled interrupts. Contents. Overview. Traditionally, a device has an interrupt line (pin) which it asserts when it wants to signal an interrupt to the host processing environment. This traditional form of interrupt signaling is an

PXI Specification Revision History This section is an overview of the revision history of the PXI specification. Revision 1.0, August 20, 1997 This is the first public revision of the PXI specification. Revision 2.0, July 28, 2000 This revision incorporates changes that include but are not limited to the following: • Transfer of the specification ownership to the PXI System Alliance

pci bridge diagram datasheet, cross reference, circuit and application notes in pdf format.

The PCI-D9-02-LP is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte …

Is there any Dell workstation with any PCI 3.3v slot or

2-Port Serial (RS-232) PCI Host Card

5 PCI Express Card Electromechanical Specification, Revision 1.1 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b

PCI Local Bus Specification Revision 2.3 PCI Bridge Architecture Specification

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth On-chip 256-byte depth FIFO in transmit and receive paths of each port.

• Compliant with PCI Express Base Specification, Revision 1.0a • Compliant with PCI Local Bus Specification, Revision 2.3 • Utilizes 100 MHz differential PCI Express Common Reference Clock or 125 MHz Single-Ended Reference Clock • Full PCI Local Bus 66 MHz/32-bit Throughput • Wake/Beacon Event Support • Robust Architecture to Minimize Latency Key Features XIO2000A EVM PCI Express

1.3 Revision History Rev. No. Description Rev. Date 1.0 Initial Release. September 15, 2008 1.1 Minor changes November 10, 2010 Meets PCI Bus Specification 2.3 and PCI Express Bus Specifications 1.1 Supports 3.3V and 5V PCI signals electrical levels (defined via jumpers) Supports swapping of all four UUTs without shutting down host computer 3.2 Debugging support Allows access to the PCI

For reference see “PCI Local Bus Specification, Revision 2.3”. 1 The PCI bus uses reflected wave switching; as a result the voltage at the pins of PCI devices could be greater than the typical ground-to-V ccvoltage range. f The user should verify that the bus switch devices meet the AC requirements in their systems. Vcc 5 V 4.3 V A0 B0 A9 B9 MMSD701T1 QS3861 Input/Output Output/Input

PI7C9X110PCIe-to-PCI Reversible BridgePage 15 of 145Pericom SemiconductorNovember 2007, Revision 2.4•Maximum payload size to 512 bytes1.2PCI / PCI-X FEATURES• datasheet search, datasheets, Datasheet search site for Electronic Components and Semiconductors, integrated circuits, diodes and other semiconductors.

PCI-X PROTOCOL ADDENDUM TO THE PCI LOCAL BUS SPECIFICATION, REV. 2.0 2 REVISION REVISION HISTORY DATE 1.0 Initial release. 9/22/99 1.0a Clarifications and typographical corrections.

Revised PCI Local Bus specification compliance to 2.3 04/1715 2.1 Updated Section 14 Configuration Registers 15-0048. PI7C8150B ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE Page 4 of 107 April 2015 – Revision 2.1 This page intentionally left blank. 15-0048. PI7C8150B ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE Page 5 of 107 April 2015 – Revision 2.1 TABLE OF CONTENTS 1 …

1 SIGNAL DEFINITIONS Diodes Incorporated

revision 2 3 pdf Pci local bus specification WordPress.com

PXI Specification Revision History This section is an overview of the revision history of the PXI specification. Revision 1.0, August 20, 1997 This is the first public revision of the PXI specification. Revision 2.0, July 28, 2000 This revision incorporates changes that include but are not limited to the following: • Transfer of the specification ownership to the PXI System Alliance

The PCI-D9-02-LP is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte …

“USB Specification” means a revision of the “Universal Serial Bus Specification,” numbered 1.0 or greater, published and made available for industry licensing by Intel and the other USB promoters.

PCI Express Card Electromechanical Specification, Revision 2.0 5 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b Universal Serial Bus Specification, Revision 2.0 10 DisplayPort Specification, Revision 1.1a SMBus Specification

PI7C9X110PCIe-to-PCI Reversible BridgePage 15 of 145Pericom SemiconductorNovember 2007, Revision 2.4•Maximum payload size to 512 bytes1.2PCI / PCI-X FEATURES• datasheet search, datasheets, Datasheet search site for Electronic Components and Semiconductors, integrated circuits, diodes and other semiconductors.

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth FIFO in …

The NI PCI-DIO-96 is fully compatible with the PCI Local Bus Specification, Revision 2.1. It also tends to operate with a known power-up state. This module can easily be used with the LabVIEW Application Builder for Windows and LabVIEW Full Development System for Windows. This model contains bias resistors that control the power-up state of the digital I/O lines. At power up, each I/O …

Compliant with PCI Local Bus Specification, Revision 2.3 . z. Supports 2 x UART serial ports . z. Add one IEEE 1284 Parallel Port on system . z. Easy Plug and Play . z. Automatically selects IRQ & I/O address . z. Built-in 16C450/550 compatible UART . z. On chip 256 byte FIFOs in transmit and receive path of each serial port . z. Serial data transfer rate up to 115200bps . z. Supports Standard

PCI Local Bus Specification Revision 2.1 June 1, 1995. Questions regarding the PCI specification be forwarded to: Questions regarding the PCI specification be forwarded to: PCI Special Interest Group

5 1.0 Introduction 1.1 Revision History Version Changes 0.80 Original version. 0.81 Grammatical corrections. 1.00 Finalized for public release. 1.01 Added the …

• Compliant with PCI Express Base Specification, Revision 1.0a • Compliant with PCI Local Bus Specification, Revision 2.3 • Utilizes 100 MHz differential PCI Express Common Reference Clock or 125 MHz Single-Ended Reference Clock • Full PCI Local Bus 66 MHz/32-bit Throughput • Wake/Beacon Event Support • Robust Architecture to Minimize Latency Key Features XIO2000A EVM PCI Express

PCI (Peripheral Component Interconnect) je standard koji određuje računarsku magistralu za priključenje perifernih uređaja na matičnu ploču računara.

Magma PE6R4 Expansion Chassis PCIe to PCI Expansion Solution for Pro Tools|HD Features • 4U rack-mountable all Prosteel enclosure • PCIe host interface card (x4)

PCI-X r1.0b PCI-X Addendum to PCI Local Bus Specification, Revision 1.0b PCI-X r2.0a PCI-X Addendum to PCI Local Bus Specification, Revision 2.0a PCI Express r1.0a PCI Express Base Specification, Revision 1.0a

pci rs232 Newegg.com

The PCI Bus OSDev Wiki

Text: Intel® 31154 133MHz PCI Bridge Datasheet Product Features s s s s s s s s s s s s s s PCI Bus Interfaces PCI Local Bus Specification, Revision 2.3 compliant PCI-to-PCI Bridge , changes to them.

DownloadPci local bus specification revision 2 3 pdf. Free Pdf Download 2 8243 pop-up ads from Windows XP . We re glad to have you here. Any idea how to get this back

PCI-SIG is committed to the development and enhancement of the PCI standard. Crediting its success to the contribution of nearly 800 members, PCI-SIG strives to provide them with the resources needed to remain competitive.

PCI Local Bus Specification Production Version Revision 2.1 June 1, 1995. Revision 2.1 REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and expansion board specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 The PCI Special Interest Group disclaims all warranties and liability for the use of this document and the information

23/09/2012 · The PCI Local Bus Specification, Revision 2.1 defines two bus cycles to access the PCI configuration space: Configuration Read and Configuration Write. Memory and I/O spaces are supported directly

Conventional PCI PCI-X ¾1.0 ¾2.0 Maintains the PCI specifications and forward-compatibility of all PCI revisions. February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0

Revision 2.3 ii REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and add-in card specification 4/30/93 2.1 Incorporated clarifications and added 66 …

ExpressLane PEX 8114 BC/BD PCI Express-to-PCI/PCI-X Bridge

pci bridge diagram datasheet & applicatoin notes

The NI PCI-DIO-96 is fully compatible with the PCI Local Bus Specification, Revision 2.1. It also tends to operate with a known power-up state. This module can easily be used with the LabVIEW Application Builder for Windows and LabVIEW Full Development System for Windows. This model contains bias resistors that control the power-up state of the digital I/O lines. At power up, each I/O …

PCI 2 DB-9 Serial (SD-PCI15025) – SystemBase SB16C1052PCI Chipset – Easy Plug & installation – Automatically Selects IRQ and I/O Address – Fully Compliant with PCI Local Bus Specification Revision 2.3

This PCI Local Bus Specification is provided as is with no.Incorporated Errata for the PCI Express Base Specification, Rev. Contact the PCI-SIG office to obtain the latest revision of this specification. 3: An Evolution of the Conventional PCI Local Bus Specification.

©PXI Systems Alliance iii PXI Express Hardware Specification Rev. 1.0 08/22/2005 PXI Express Hardware Specification Revision History This section is an overview of the revision history of the PXI Express Hardware Specification.

A PCI interface adapter provides the interface between the controlling PCI bus and the internal local controller (Figure 1). The control interface conforms to IEEE PCI local bus specification Revision 2.3…

• PCI Local Bus Specification, Revision 2.3, PCI Special Interest Group • PXI Hardware Specification, Revision 2.2, PXI Systems Alliance • PXI Software Specification, Revision 2.1, PXI Systems Alliance

The PCI-D9-02-LP is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte …

PXI Specification PCI eXtensions for Instrumentation

PCI-D9-02-LP Datasheet assets.tripplite.com

PCI Local Bus Specification Revision 2.3 PCI Bridge Architecture Specification

Compliant with PCI Local Bus Specification, Revision 2.3 . z. Supports 2 x UART serial ports . z. Add one IEEE 1284 Parallel Port on system . z. Easy Plug and Play . z. Automatically selects IRQ & I/O address . z. Built-in 16C450/550 compatible UART . z. On chip 256 byte FIFOs in transmit and receive path of each serial port . z. Serial data transfer rate up to 115200bps . z. Supports Standard

PCI (Peripheral Component Interconnect) je standard koji određuje računarsku magistralu za priključenje perifernih uređaja na matičnu ploču računara.

PCI Express Card Electromechanical Specification, Revision 2.0 5 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b Universal Serial Bus Specification, Revision 2.0 10 DisplayPort Specification, Revision 1.1a SMBus Specification

5 1.0 Introduction 1.1 Revision History Version Changes 0.80 Original version. 0.81 Grammatical corrections. 1.00 Finalized for public release. 1.01 Added the …

pci bridge diagram datasheet, cross reference, circuit and application notes in pdf format.

21154 PCI-to-PCI Bridge Datasheet Product Features Complies fully with the PCI Local Bus Specification, Revision 2.1 Complies fully with the PCI Power Management Specification , Revision 1.01 Supports 64-bit extension signals on the primary and secondary interfaces Implements delayed transactions for all PCI configuration, I/O, and memory read commands–up to three transactions …

VANTEC UGT-PC2S1P USER MANUAL Pdf Download.

Is there any Dell workstation with any PCI 3.3v slot or

They operate at 33 MHz, and are fully compliant with the PCI Local Bus Specification, Revision 2.2, and are compatible with Revision 2.3. The cards support both the 3.3 V and 5 V signaling environments, defined by the PCI Local Bus Specification. The cards are considered universal add-in cards that are capable of detecting the signaling environment and adapting themselves to that environment.

23/09/2012 · The PCI Local Bus Specification, Revision 2.1 defines two bus cycles to access the PCI configuration space: Configuration Read and Configuration Write. Memory and I/O spaces are supported directly

PXI Specification Revision History This section is an overview of the revision history of the PXI specification. Revision 1.0, August 20, 1997 This is the first public revision of the PXI specification. Revision 2.0, July 28, 2000 This revision incorporates changes that include but are not limited to the following: • Transfer of the specification ownership to the PXI System Alliance

PCI Express Card Electromechanical Specification, Revision 2.0 5 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b Universal Serial Bus Specification, Revision 2.0 10 DisplayPort Specification, Revision 1.1a SMBus Specification

For reference see “PCI Local Bus Specification, Revision 2.3”. 1 The PCI bus uses reflected wave switching; as a result the voltage at the pins of PCI devices could be greater than the typical ground-to-V ccvoltage range. f The user should verify that the bus switch devices meet the AC requirements in their systems. Vcc 5 V 4.3 V A0 B0 A9 B9 MMSD701T1 QS3861 Input/Output Output/Input

specification establishes the minimum.PCI Local Bus Specification, Revision 2. 3, PCI Special Interest Group. The Ethernet Port 2 The Ethernet Port 2 block consists of an Intel I210-IT Gigabit Ethernet Connection.Dec 18, 1998.

PCI Local Bus Specification, Revision 2.0 April 30, 1993 Standard BIOS 32-bit Service Directory Proposal, Revision 0.4 May 24, 1993 (available from Phoenix Technologies Ltd., Norwood, MA)

Compatible with the PCI Local Bus Specification, Revision 2. The PCI bus is the de-facto standard bus for current-generation personal computers. The PCI bus is a 32- or 64-bit wide bus with multiplexed address and data lines. Page 5.at either PCI pathophysiology diabetic foot pdf bus, the input clock frequency at signal PCLK. Internal plane 3 5 V with 12V islands. 3 PCI Local Bus specification

©PXI Systems Alliance iii PXI Express Hardware Specification Rev. 1.0 08/22/2005 PXI Express Hardware Specification Revision History This section is an overview of the revision history of the PXI Express Hardware Specification.

5 1.0 Introduction 1.1 Revision History Version Changes 0.80 Original version. 0.81 Grammatical corrections. 1.00 Finalized for public release. 1.01 Added the …

• PCI Local Bus Specification, Revision 2.3, PCI Special Interest Group • PXI Hardware Specification, Revision 2.2, PXI Systems Alliance • PXI Software Specification, Revision 2.1, PXI Systems Alliance

• PC interface compliant with PCI express base specification, revision 1.1 • form factor F2: Full-mini with bottom-side keep outs • dimensions according to PCI express Mini Card electromechanical specification, revision

Magma 7-Slot PCI Express Board-Set (Gen2 x8 Speed)

PCI-D9-02-LP Datasheet assets.tripplite.com

For reference see “PCI Local Bus Specification, Revision 2.3”. 1 The PCI bus uses reflected wave switching; as a result the voltage at the pins of PCI devices could be greater than the typical ground-to-V ccvoltage range. f The user should verify that the bus switch devices meet the AC requirements in their systems. Vcc 5 V 4.3 V A0 B0 A9 B9 MMSD701T1 QS3861 Input/Output Output/Input

Compatible with the PCI Local Bus Specification, Revision 2. The PCI bus is the de-facto standard bus for current-generation personal computers. The PCI bus is a 32- or 64-bit wide bus with multiplexed address and data lines. Page 5.at either PCI pathophysiology diabetic foot pdf bus, the input clock frequency at signal PCLK. Internal plane 3 5 V with 12V islands. 3 PCI Local Bus specification

PCI Express Base Specification Revision 1.0 April 29, 2002. REVISION REVISION HISTORY DATE 1.0 Initial release. 4/29/02 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein

• PCI Local Bus Specification, revision 2.3; PCI-X Protocol addendum to the PCI Local Bus Specification, revision 2.0a; PCI-X electrical and Mechanical addendum (revision 2.0a) to the PCI Local Bus Specification; PCI Bus Power Management Interface Specification, revision 1.1; PCI …

• PCI low profile 2x port IEEE 1394B 1x port IEEE 1394A firewire card • Compliant with PCI Local Bus Specification Revision 2.3 • Support PCI Bus Power Management Interface Specification Revision …

5 PCI Express Card Electromechanical Specification, Revision 1.1 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b

pci bridge diagram datasheet, cross reference, circuit and application notes in pdf format.

While the PCI Local Bus Specification, Revision 3.0 (PCI 3.0) is quite complete with a solid definition of protocols, electrical characteristics, and mechanical form factors, no provision was made for

Asynchronous PCI-to-PCI Bridge (Rev. A TI.com

Universal Host Controller Interface (UHCI) Design Guide

A PCI interface adapter provides the interface between the controlling PCI bus and the internal local controller (Figure 1). The control interface conforms to IEEE PCI local bus specification Revision 2.3…

For reference see “PCI Local Bus Specification, Revision 2.3”. 1 The PCI bus uses reflected wave switching; as a result the voltage at the pins of PCI devices could be greater than the typical ground-to-V ccvoltage range. f The user should verify that the bus switch devices meet the AC requirements in their systems. Vcc 5 V 4.3 V A0 B0 A9 B9 MMSD701T1 QS3861 Input/Output Output/Input

• PC interface compliant with PCI express base specification, revision 1.1 • form factor F2: Full-mini with bottom-side keep outs • dimensions according to PCI express Mini Card electromechanical specification, revision

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth FIFO in …

Compliant with PCI Local Bus Specification, Revision 2.3 . z. Supports 2 x UART serial ports . z. Add one IEEE 1284 Parallel Port on system . z. Easy Plug and Play . z. Automatically selects IRQ & I/O address . z. Built-in 16C450/550 compatible UART . z. On chip 256 byte FIFOs in transmit and receive path of each serial port . z. Serial data transfer rate up to 115200bps . z. Supports Standard

Compatible with the PCI Local Bus Specification, Revision 2. The PCI bus is the de-facto standard bus for current-generation personal computers. The PCI bus is a 32- or 64-bit wide bus with multiplexed address and data lines. Page 5.at either PCI pathophysiology diabetic foot pdf bus, the input clock frequency at signal PCLK. Internal plane 3 5 V with 12V islands. 3 PCI Local Bus specification

Management Component Transport Protocol (MCTP) KCS Transport Binding Specification (DSP0256) was prepared by the PMCI Subgroup of the Pre-OS Working Group. DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems

PI7C9X110PCIe-to-PCI Reversible BridgePage 15 of 145Pericom SemiconductorNovember 2007, Revision 2.4•Maximum payload size to 512 bytes1.2PCI / PCI-X FEATURES• datasheet search, datasheets, Datasheet search site for Electronic Components and Semiconductors, integrated circuits, diodes and other semiconductors.

2-Port DB9 (RS-232) Serial PCI Card with 16550 UART Full

PCI_Express_Mini_CEM_2_0.pdf Electrical Connector Usb

specification establishes the minimum.PCI Local Bus Specification, Revision 2. 3, PCI Special Interest Group. The Ethernet Port 2 The Ethernet Port 2 block consists of an Intel I210-IT Gigabit Ethernet Connection.Dec 18, 1998.

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth On-chip 256-byte depth FIFO in transmit and receive paths of each port.

View PCI.Local.Bus.Specification.Revision.3.0 from EE 272 at San Jose State University. PCI Local Bus Specification Revision 3.0 August 12, 2002 PCI SPECIFICATIONS REVISION REVISION PCI Local Bus Specification Revision 3.0 August 12, 2002 PCI SPECIFICATIONS REVISION REVISION

While the PCI Local Bus Specification, Revision 3.0 (PCI 3.0) is quite complete with a solid definition of protocols, electrical characteristics, and mechanical form factors, no provision was made for

Revision 2.3 is a huge change to the PCI Local Bus Specification. Revision 2.3 makes a significant step in migrating the PCI bus from the original 5.0 volt signaling to a 3.3 volt signaling bus. Revision 2.3 supports the 5V and 3.3V keyed system board connectors (as did revision 2.2) but

PCI (Peripheral Component Interconnect) je standard koji određuje računarsku magistralu za priključenje perifernih uređaja na matičnu ploču računara.

• PCI Local Bus Specification, revision 2.3; PCI-X Protocol addendum to the PCI Local Bus Specification, revision 2.0a; PCI-X electrical and Mechanical addendum (revision 2.0a) to the PCI Local Bus Specification; PCI Bus Power Management Interface Specification, revision 1.1; PCI …

PCI Local Bus Specification Revision 2.1 June 1, 1995. Questions regarding the PCI specification be forwarded to: Questions regarding the PCI specification be forwarded to: PCI Special Interest Group

This PCI Local Bus Specification is provided as is with no.Incorporated Errata for the PCI Express Base Specification, Rev. Contact the PCI-SIG office to obtain the latest revision of this specification. 3: An Evolution of the Conventional PCI Local Bus Specification.

The NI PCI-DIO-96 is fully compatible with the PCI Local Bus Specification, Revision 2.1. It also tends to operate with a known power-up state. This module can easily be used with the LabVIEW Application Builder for Windows and LabVIEW Full Development System for Windows. This model contains bias resistors that control the power-up state of the digital I/O lines. At power up, each I/O …

TIMING, TEST & MEASUREMENT bc635PCI-U PCI Time & Frequency Processor KEY FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

5 PCI Express Card Electromechanical Specification, Revision 1.1 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b

A PCI interface adapter provides the interface between the controlling PCI bus and the internal local controller (Figure 1). The control interface conforms to IEEE PCI local bus specification Revision 2.3…

• PC interface compliant with PCI express base specification, revision 1.1 • form factor F2: Full-mini with bottom-side keep outs • dimensions according to PCI express Mini Card electromechanical specification, revision

Syba Web

Management Component Transport Protocol (MCTP) Host

This document specifies the application of Open Firmware to the PCI Local Bus, including PCI-specific require-ments and practices for address format, interrupts, probing, and related properties and methods. The core requirements and practices specified by Open Firmware must be augmented by system-specific require-ments to form a complete specification for the firmware for a particular system

PCI (Peripheral Component Interconnect) je standard koji određuje računarsku magistralu za priključenje perifernih uređaja na matičnu ploču računara.

PCI-SIG is committed to the development and enhancement of the PCI standard. Crediting its success to the contribution of nearly 800 members, PCI-SIG strives to provide them with the resources needed to remain competitive.

Revision 2.3 is a change to the PCI Local Bus Specification. Revision 2.3 makes a significant step in migrating the PCI bus from the original 5.0 volt signaling to a 3.3 volt signaling bus. Revision 2.3 supports the 5V and 3.3V keyed system board connectors (as did revision 2.2) but

Compliant with PCI Local Bus Specification, Revision 2.3 . z. Supports 2 x UART serial ports . z. Add one IEEE 1284 Parallel Port on system . z. Easy Plug and Play . z. Automatically selects IRQ & I/O address . z. Built-in 16C450/550 compatible UART . z. On chip 256 byte FIFOs in transmit and receive path of each serial port . z. Serial data transfer rate up to 115200bps . z. Supports Standard

• PCI Local Bus Specification, revision 2.3; PCI-X Protocol addendum to the PCI Local Bus Specification, revision 2.0a; PCI-X electrical and Mechanical addendum (revision 2.0a) to the PCI Local Bus Specification; PCI Bus Power Management Interface Specification, revision 1.1; PCI …

DownloadPci local bus specification revision 2 3 pdf. Free Pdf Download 2 8243 pop-up ads from Windows XP . We re glad to have you here. Any idea how to get this back

Text: Intel® 31154 133MHz PCI Bridge Datasheet Product Features s s s s s s s s s s s s s s PCI Bus Interfaces PCI Local Bus Specification, Revision 2.3 compliant PCI-to-PCI Bridge , changes to them.

23/09/2012 · The PCI Local Bus Specification, Revision 2.1 defines two bus cycles to access the PCI configuration space: Configuration Read and Configuration Write. Memory and I/O spaces are supported directly

PCI Local Bus Specification Revision 2.1 June 1, 1995. Questions regarding the PCI specification be forwarded to: Questions regarding the PCI specification be forwarded to: PCI Special Interest Group

TIMING, TEST & MEASUREMENT bc635PCI-U PCI Time & Frequency Processor KEY FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

The PCI2050 bridge is compliant with the PCI Local Bus Specification , and can be used to overcome the electrical loading limits of 10 devices per PCI bus and one PCI device per expansion slot by creating hierarchical buses.

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth On-chip 256-byte depth FIFO in transmit and receive paths of each port.

PXI Specification Revision History This section is an overview of the revision history of the PXI specification. Revision 1.0, August 20, 1997 This is the first public revision of the PXI specification. Revision 2.0, July 28, 2000 This revision incorporates changes that include but are not limited to the following: • Transfer of the specification ownership to the PXI System Alliance

PCI Expansion Backplane Amfeltec

pci bridge diagram datasheet & applicatoin notes

For reference see “PCI Local Bus Specification, Revision 2.3”. 1 The PCI bus uses reflected wave switching; as a result the voltage at the pins of PCI devices could be greater than the typical ground-to-V ccvoltage range. f The user should verify that the bus switch devices meet the AC requirements in their systems. Vcc 5 V 4.3 V A0 B0 A9 B9 MMSD701T1 QS3861 Input/Output Output/Input

Revision 1.1 9 Preface Scope This specification defines the behavior of a compliant PCI-to-PCI bridge. A PCI-to-PCI bridge that conforms to this specification and the PCI Local Bus Specification is a …

PCI-X r1.0b PCI-X Addendum to PCI Local Bus Specification, Revision 1.0b PCI-X r2.0a PCI-X Addendum to PCI Local Bus Specification, Revision 2.0a PCI Express r1.0a PCI Express Base Specification, Revision 1.0a

bc635PCI-U PCI Time & Frequency Processor KEY ®FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

PCI Express Base Specification Revision 1.0 April 29, 2002. REVISION REVISION HISTORY DATE 1.0 Initial release. 4/29/02 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein

“USB Specification” means a revision of the “Universal Serial Bus Specification,” numbered 1.0 or greater, published and made available for industry licensing by Intel and the other USB promoters.

©PXI Systems Alliance iii PXI Express Hardware Specification Rev. 1.0 08/22/2005 PXI Express Hardware Specification Revision History This section is an overview of the revision history of the PXI Express Hardware Specification.

Message signaled interrupts are supported in PCI bus since its version 2.2, and in later available PCI Express bus. Some non-PCI architectures also use message signaled interrupts. Contents. Overview. Traditionally, a device has an interrupt line (pin) which it asserts when it wants to signal an interrupt to the host processing environment. This traditional form of interrupt signaling is an

PCI-X PROTOCOL ADDENDUM TO THE PCI LOCAL BUS SPECIFICATION, REV. 2.0 2 REVISION REVISION HISTORY DATE 1.0 Initial release. 9/22/99 1.0a Clarifications and typographical corrections.

Features and Benefits Compliant with PCI Local Bus Specification, Revision 2.3 Supports 2 x UART serial ports Add one IEEE 1284 Parallel Port on system Easy Plug and Play Automatically selects IRQ & I/O address Built-in 16C450/550 compatible UART On chip 256 byte FIFOs in transmit and receive path of each serial port Serial data transfer rate up to 115200bps Supports Standard Parallel Port

A PCI interface adapter provides the interface between the controlling PCI bus and the internal local controller (Figure 1). The control interface conforms to IEEE PCI local bus specification Revision 2.3…

PCI Local Bus Specification Production Version Revision 2.1 June 1, 1995. Revision 2.1 REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and expansion board specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 The PCI Special Interest Group disclaims all warranties and liability for the use of this document and the information

View PCI.Local.Bus.Specification.Revision.3.0 from EE 272 at San Jose State University. PCI Local Bus Specification Revision 3.0 August 12, 2002 PCI SPECIFICATIONS REVISION REVISION PCI Local Bus Specification Revision 3.0 August 12, 2002 PCI SPECIFICATIONS REVISION REVISION

Revision 2.3 is a huge change to the PCI Local Bus Specification. Revision 2.3 makes a significant step in migrating the PCI bus from the original 5.0 volt signaling to a 3.3 volt signaling bus. Revision 2.3 supports the 5V and 3.3V keyed system board connectors (as did revision 2.2) but

PCI Local Bus Specification, Revision 2.0 April 30, 1993 Standard BIOS 32-bit Service Directory Proposal, Revision 0.4 May 24, 1993 (available from Phoenix Technologies Ltd., Norwood, MA)

Dump error with wireless PCI card on GX520 Dell Community

-5 PXI Express Hardware Specification pxisa.org

DownloadPci local bus specification revision 2 3 pdf. Free Pdf Download 2 8243 pop-up ads from Windows XP . We re glad to have you here. Any idea how to get this back

Conventional PCI PCI-X ¾1.0 ¾2.0 Maintains the PCI specifications and forward-compatibility of all PCI revisions. February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0

Revision 2.3 ii REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and add-in card specification 4/30/93 2.1 Incorporated clarifications and added 66 …

specification establishes the minimum.PCI Local Bus Specification, Revision 2. 3, PCI Special Interest Group. The Ethernet Port 2 The Ethernet Port 2 block consists of an Intel I210-IT Gigabit Ethernet Connection.Dec 18, 1998.

The NI PCI-DIO-96 is fully compatible with the PCI Local Bus Specification, Revision 2.1. It also tends to operate with a known power-up state. This module can easily be used with the LabVIEW Application Builder for Windows and LabVIEW Full Development System for Windows. This model contains bias resistors that control the power-up state of the digital I/O lines. At power up, each I/O …

A value of 0x01 is reserved as of revision 3.0 of the PCI Local Bus Specification. In earlier versions it was used to support memory space below 1MB (16-bit wide base register that can be mapped anywhere in the 16-bit Memory Space).

Contact the PCI-SIG office to obtain the latest revision of this specification. Questions regarding the PCI Express Base Specification or membership in PCI-SIG may be forwarded to: Membership Services

Revision 1.1 9 Preface Scope This specification defines the behavior of a compliant PCI-to-PCI bridge. A PCI-to-PCI bridge that conforms to this specification and the PCI Local Bus Specification is a …

©PXI Systems Alliance iii PXI Express Hardware Specification Rev. 1.0 08/22/2005 PXI Express Hardware Specification Revision History This section is an overview of the revision history of the PXI Express Hardware Specification.

PCI Local Bus Specification Revision 2.3 PCI Bridge Architecture Specification

PCI-X r1.0b PCI-X Addendum to PCI Local Bus Specification, Revision 1.0b PCI-X r2.0a PCI-X Addendum to PCI Local Bus Specification, Revision 2.0a PCI Express r1.0a PCI Express Base Specification, Revision 1.0a

PCI Local Bus Specification Revision 2.1 June 1, 1995. Questions regarding the PCI specification be forwarded to: Questions regarding the PCI specification be forwarded to: PCI Special Interest Group

PCI Local Bus Specification, Revision 2.0 April 30, 1993 Standard BIOS 32-bit Service Directory Proposal, Revision 0.4 May 24, 1993 (available from Phoenix Technologies Ltd., Norwood, MA)

bc635PCI-U PCI Time & Frequency Processor KEY ®FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

PXI Specification Revision History This section is an overview of the revision history of the PXI specification. Revision 1.0, August 20, 1997 This is the first public revision of the PXI specification. Revision 2.0, July 28, 2000 This revision incorporates changes that include but are not limited to the following: • Transfer of the specification ownership to the PXI System Alliance

TIMING, TEST & MEASUREMENT bc635PCI-U PCI Time & Frequency Processor KEY FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

PCI Expansion Backplane Amfeltec

Asynchronous PCI-to-PCI Bridge (Rev. A TI.com

Konvencijalni PCI Wikipedia

TIMING, TEST & MEASUREMENT bc635PCI-U PCI Time & Frequency Processor KEY FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

Data Sheet 2400 Series PCIe-to-4Gbps and PCI-X-to-4Gbps

Compliant with PCI Local Bus Specification, Revision 2.3 . z. Supports 2 x UART serial ports . z. Add one IEEE 1284 Parallel Port on system . z. Easy Plug and Play . z. Automatically selects IRQ & I/O address . z. Built-in 16C450/550 compatible UART . z. On chip 256 byte FIFOs in transmit and receive path of each serial port . z. Serial data transfer rate up to 115200bps . z. Supports Standard

PCI_Express_Mini_CEM_2_0.pdf Electrical Connector Usb

PCI-X Protocol Addendum to the PCI Local Bus Specification

• PCI Local Bus Specification, Revision 2.3, PCI Special Interest Group • PXI Hardware Specification, Revision 2.2, PXI Systems Alliance • PXI Software Specification, Revision 2.1, PXI Systems Alliance

Syba Web

1 SIGNAL DEFINITIONS Diodes Incorporated

Pci bus specification 3 5 pdf afylinaxij.files.wordpress.com

Conventional PCI PCI-X ¾1.0 ¾2.0 Maintains the PCI specifications and forward-compatibility of all PCI revisions. February 2003 Page 5 PCI Technology Conventional PCI ¾Initial PCI 1.0 proposal by Intel in 1991 ¾Introduced by PCI-SIG as PCI 2.0 in 1993 ¾Version 2.1 approved in 1995 ¾Recent version 2.3 approved in March 2002 PCI-X ¾Version 1.0 approved in September 1999 ¾Version 2.0

Pci bus specification 3 5 pdf afylinaxij.files.wordpress.com

pci rs232 Newegg.com

VANTEC UGT-PC2S1P USER MANUAL Pdf Download.

PCI Local Bus Specification Revision 2.1 June 1, 1995. Questions regarding the PCI specification be forwarded to: Questions regarding the PCI specification be forwarded to: PCI Special Interest Group

PXI Specification PCI eXtensions for Instrumentation

Data Sheet 2400 Series PCIe-to-4Gbps and PCI-X-to-4Gbps

1 SIGNAL DEFINITIONS Diodes Incorporated

Revised PCI Local Bus specification compliance to 2.3 04/1715 2.1 Updated Section 14 Configuration Registers 15-0048. PI7C8150B ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE Page 4 of 107 April 2015 – Revision 2.1 This page intentionally left blank. 15-0048. PI7C8150B ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE Page 5 of 107 April 2015 – Revision 2.1 TABLE OF CONTENTS 1 …

How to access the chipset’s registers Ars Technica OpenForum

PCI Technology Overview Digi International

Features and Benefits Compliant with PCI Local Bus Specification, Revision 2.3 Supports 2 x UART serial ports Add one IEEE 1284 Parallel Port on system Easy Plug and Play Automatically selects IRQ & I/O address Built-in 16C450/550 compatible UART On chip 256 byte FIFOs in transmit and receive path of each serial port Serial data transfer rate up to 115200bps Supports Standard Parallel Port

Management Component Transport Protocol (MCTP) Host

INTEL BLKDG41WV TECHNICAL PRODUCT SPECIFICATION Pdf

The PCI-D9-02-LP is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte …

Vantec UGT-PC2S1P Serial and Parallel PCI Card Manual

bc635PCI-U PCI Time & Frequency Processor KEY ®FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

PCI bridge datasheet & applicatoin notes Datasheet Archive

Data Sheet bc635PCI-U microsemi.com

A value of 0x01 is reserved as of revision 3.0 of the PCI Local Bus Specification. In earlier versions it was used to support memory space below 1MB (16-bit wide base register that can be mapped anywhere in the 16-bit Memory Space).

560-5907-U SYMMETRICOM INC 560-5907-U Plug-in Card

How to access the chipset’s registers Ars Technica OpenForum

Connecting Altera 3.3-V PCI devices to a 5-V PCI Bus

Compatible with the PCI Local Bus Specification, Revision 2. The PCI bus is the de-facto standard bus for current-generation personal computers. The PCI bus is a 32- or 64-bit wide bus with multiplexed address and data lines. Page 5.at either PCI pathophysiology diabetic foot pdf bus, the input clock frequency at signal PCLK. Internal plane 3 5 V with 12V islands. 3 PCI Local Bus specification

-5 PXI Express Hardware Specification pxisa.org

The PCI-D9-02 is fully compliant with PCI Local Bus Specification Revision 2.3 and compatible with industrial standard 16550 UART. On-chip 256-byte depth FIFO in …

Magma 7-Slot PCI Express Board-Set (Gen2 x8 Speed)

How to access the chipset’s registers Ars Technica OpenForum

Syba Web

TIMING, TEST & MEASUREMENT bc635PCI-U PCI Time & Frequency Processor KEY FEATURES • PCI Local Bus Operation • 3.3V and 5.0V Universal Signaling • IRIG A, B and IEEE 1344

ExpressLane PEX 8114 BC/BD PCI Express-to-PCI/PCI-X Bridge

The PCI Bus OSDev Wiki

Konvencijalni PCI Wikipedia

Management Component Transport Protocol (MCTP) KCS Transport Binding Specification (DSP0256) was prepared by the PMCI Subgroup of the Pre-OS Working Group. DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems

16AO16 Analog Out Differential 16-Bit 16-Chan PCI

PCI-X PROTOCOL ADDENDUM TO THE PCI LOCAL BUS SPECIFICATION, REV. 2.0 2 REVISION REVISION HISTORY DATE 1.0 Initial release. 9/22/99 1.0a Clarifications and typographical corrections.

ExpressLane PEX 8114 BC/BD PCI Express-to-PCI/PCI-X Bridge

Magma 7-Slot PCI Express Board-Set (Gen2 x8 Speed)

Message Signaled Interrupts Wikipedia

• PCI Local Bus Specification, revision 2.3; PCI-X Protocol addendum to the PCI Local Bus Specification, revision 2.0a; PCI-X electrical and Mechanical addendum (revision 2.0a) to the PCI Local Bus Specification; PCI Bus Power Management Interface Specification, revision 1.1; PCI …

PCI Expansion Backplane Amfeltec

PCI SYBA 2 DB-9 Serial (SD-PCI15025) Mini-Box.com

5 1.0 Introduction 1.1 Revision History Version Changes 0.80 Original version. 0.81 Grammatical corrections. 1.00 Finalized for public release. 1.01 Added the …

bc635PCI-U Vox Technologies

23/09/2012 · The PCI Local Bus Specification, Revision 2.1 defines two bus cycles to access the PCI configuration space: Configuration Read and Configuration Write. Memory and I/O spaces are supported directly

Konvencijalni PCI Wikipedia

PXI Specification PCI eXtensions for Instrumentation

Asynchronous PCI-to-PCI Bridge (Rev. A TI.com

• PCI low profile 2x port IEEE 1394B + 1x port IEEE 1394A firewire card • Compliant with PCI Local Bus Specification Revision 2.3 • Support PCI Bus Power Management Interface Specification Revision …

Version 1.01 January 11 1996 ACPICA

PI7C9X110BNBE datasheet(15/145 Pages) PERICOM PCI

pci bridge diagram datasheet & applicatoin notes

PCI Express Base Specification Revision 1.0 April 29, 2002. REVISION REVISION HISTORY DATE 1.0 Initial release. 4/29/02 PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein

PCI-To-PCI Bridge (Rev. B) Digi-Key

5 PCI Express Card Electromechanical Specification, Revision 1.1 PCI Local Bus Specification, Revision 2.3 Mini PCI Specification, Revision 1.0 PCI Bus Power Management Interface Specification, Revision 1.2 Advanced Configuration and Power Interface Specification, Revision 2.0b

PCI.Local.Bus.Specification.Revision.3.0 PCI Local Bus

PCI-SIG is committed to the development and enhancement of the PCI standard. Crediting its success to the contribution of nearly 800 members, PCI-SIG strives to provide them with the resources needed to remain competitive.

Is there any Dell workstation with any PCI 3.3v slot or

16AO16 Analog Out Differential 16-Bit 16-Chan PCI

Dump error with wireless PCI card on GX520 Dell Community

Specifications: Compliant with PCI Local Bus Specification, Revision 2.3 Chip: Moschip MCS9865 Full support for DOS and Windows based software PCI IRQ sharing feature reduces IRQ conflicts Ports: 2x serial ports (9-pin, RS-232, 16550 UART) RoHS compliant

Pci local bus specification revision 2 2 pdf WordPress.com

PCI.Local.Bus.Specification.Revision.3.0 PCI Local Bus

This document specifies the application of Open Firmware to the PCI Local Bus, including PCI-specific require-ments and practices for address format, interrupts, probing, and related properties and methods. The core requirements and practices specified by Open Firmware must be augmented by system-specific require-ments to form a complete specification for the firmware for a particular system

Management Component Transport Protocol (MCTP) Host

560-5907-U SYMMETRICOM INC 560-5907-U Plug-in Card

How to access the chipset’s registers Ars Technica OpenForum